Intel

®

IXP42X product line and IXC1100 control plane processors—Internal Bus Performance

Monitoring Unit (IBPMU)

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

376 Order Number: 252480-006US

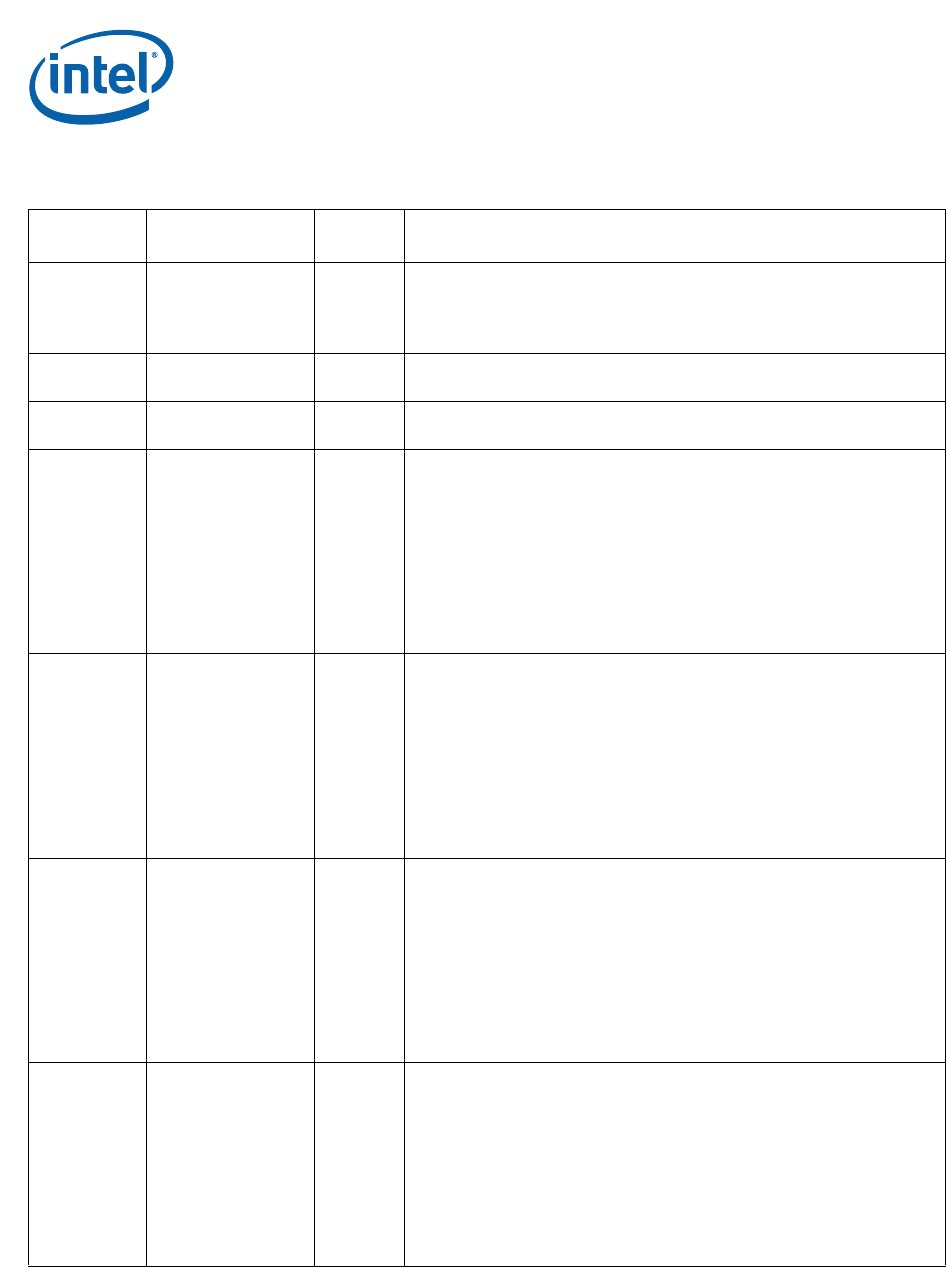

Table 142. North and South Modes Event Descriptions (Sheet 1 of 2)

Event

Bus

Components

Type Description

Bus_idle

North AHB

South AHB

Duration

Increments the counter every AHB Bus idle cycle. An idle cycle occurs when

there is no activity on the bus due to data being transferred and the bus is

not in an overhead cycle. An overhead cycle is a cycle when an initiator

owns the bus, however the initiator is unable to send data or the target is

unable to receive data - hence no data is transferred.

Bus_Write

North AHB

South AHB

Duration

Increments the counter on every AHB Bus Write data cycle. This enables

calculation of data utilization of the Write data bus.

Bus_Read

North AHB

South AHB

Duration

Increments the counter on every AHB Bus Read data cycle. This enables

calculation of data utilization of the Write data bus.

MstrX_Req

North:

•WAN/Voice NPE

• Ethernet NPE A

• Ethernet NPE B

South:

•Intel XScale

processor

• AHB/AHB Bridge

• PCI Bus

•AHB/APB Bridge

Duration

Counts the number of clocks spent by a master acquiring the AHB bus.

The counter increments on every clock cycle after the master has requested

use of the bus but has not actively driven the bus as an initiator. This is an

event primitive, used in conjunction with another event primitive (number

of grants granted) to calculate the average acquisition latency.

MstrX_Own

North:

•WAN/Voice NPE

• Ethernet NPE A

• Ethernet NPE B

South:

•Intel XScale

processor

• AHB/AHB Bridge

• PCI Bus

•AHB/APB Bridge

Duration

Counts the duration for which the master is the initiator on the AHB bus.

The counter increments on every clock cycle during which the master is the

bus initiator.

MstrX_Write

North:

•WAN/Voice NPE

• Ethernet NPE A

• Ethernet NPE B

South:

•Intel XScale

processor

• AHB/AHB Bridge

•PCI Bus

•AHB/APB Bridge

Duration

Increments counter every AHB bus write data cycle where the master is the

initiator.

MstrX_Read

North:

•WAN/Voice NPE

• Ethernet NPE A

• Ethernet NPE B

South:

•Intel XScale

processor

• AHB/AHB Bridge

• PCI Bus

•AHB/APB Bridge

Duration

Increments counter every AHB bus read data cycle where the master is the

initiator.