Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 135

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

3.7.2.3 Performance Monitor Control Register

(PMNC)

The performance monitor control register (PMNC) is a coprocessor register that:

• Contains the PMU ID

• Extends CCNT counting by six more bits (cycles between counter rollover = 2

38

)

• Resets all counters to zero

• And enables the entire mechanism

Table 56 shows the format of the PMNC register.

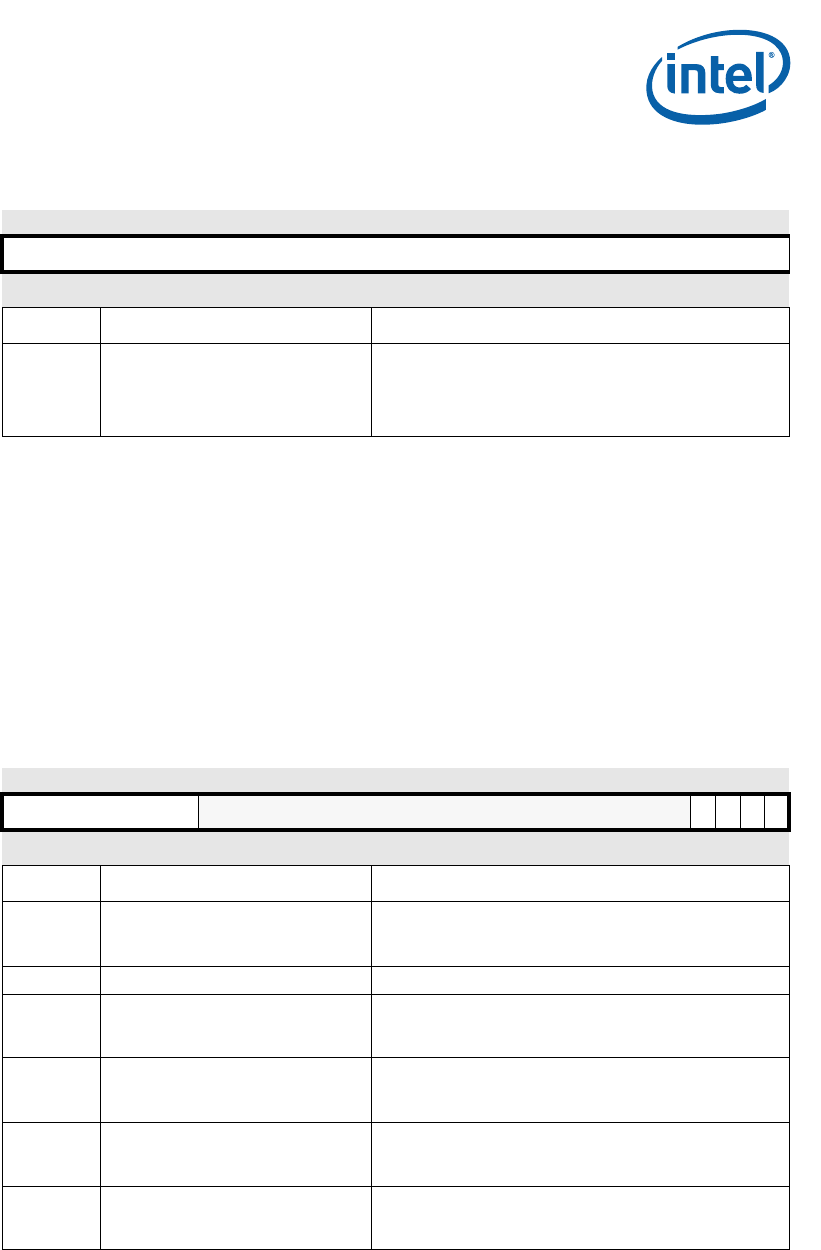

Table 55. Performance Monitor Count Register (PMN0 - PMN3)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Event Counter

reset value: unpredictable

Bits Access Description

31:0 Read / Write

32-bit event counter - Reset to ‘0’ by PMNC register.

When an event counter reaches its maximum value

0xFFFF,FFFF, the next event it needs to count will cause it

to roll over to zero and generate an interrupt request if

enabled.

Table 56. Performance Monitor Control Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

ID DCPE

reset value: E and ID are 0, others unpredictable

Bits Access Description

31:24 Read / Write Ignored

Performance Monitor Identification (ID) -

Intel

®

IXP42X product line and IXC1100 control plane

processors = 0x14

23:4 Read-unpredictable / Write-as-0 Reserved

3Read / Write

Clock Counter Divider (D) -

0 = CCNT counts every processor clock cycle

1 = CCNT counts every 64

th

processor clock cycle

2 Read-unpredictable / Write

Clock Counter Reset (C) -

0 = no action

1 = reset the clock counter to ‘0x0’

1 Read-unpredictable / Write

Performance Counter Reset (P) -

0 = no action

1 = reset all performance counters to ‘0x0’

0Read / Write

Enable (E) -

0 = all counters are disabled

1 = all counters are enabled