Intel

®

IXP42X product line and IXC1100 control plane processors—Universal Serial Bus (USB)

v1.1 Device Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

482 Order Number: 252480-006US

18.5.1.4 Resume Interrupt Request (RESIR)

The resume interrupt request bit is set if the SRM bit in the UDC control register is

cleared, the UDC is currently in the suspended state, and the USB is driven with

resume signalling.

18.5.1.5 Suspend Interrupt Request (SUSIR)

The suspend interrupt request register is set when the USB remains idle for more than

6 ms. The SUSIR bit retains state so software can determine that the USB is idle. If

SRM is 0, SUSIR being set will not generate an interrupt but status continues to be

updated.

18.5.1.6 Suspend/Resume Interrupt Mask (SRM)

The suspend/resume interrupt mask (SRM) masks or enables the suspend interrupt

request to the interrupt controller. When SRM is 1, the interrupt is masked and the

setting of SUSIR will not generate an interrupt. When SRM is 0, the setting of SUSIR

generates an interrupt when the USB is idle for more than 6 ms.

Programming SRM does not affect the state of SUSIR.

18.5.1.7 Reset Interrupt Request (RSTIR)

The reset interrupt request register is set when the host issues a reset. When the host

issues a reset, the entire UDC is reset. The RSTIR bit retains its state so software can

determine that the design was reset. If REM is 0, RSTIR being set does not generate an

interrupt but status continues to be updated.

18.5.1.8 Reset Interrupt Mask (REM)

The reset interrupt mask (REM) masks or enables the reset interrupt request to the

interrupt controller. When REM is 1, the interrupt is masked and the setting of RSTIR

does not generate an interrupt. When REM is 0, the RSTIR setting generates an

interrupt when the USB host controller issues an UDC reset.

Programming REM does not affect the state of RSTIR.

The UDE bit is cleared to 0, which disables the UDC following a Intel XScale

®

processor

reset. Writes to reserved bits are ignored and reads return zeros.

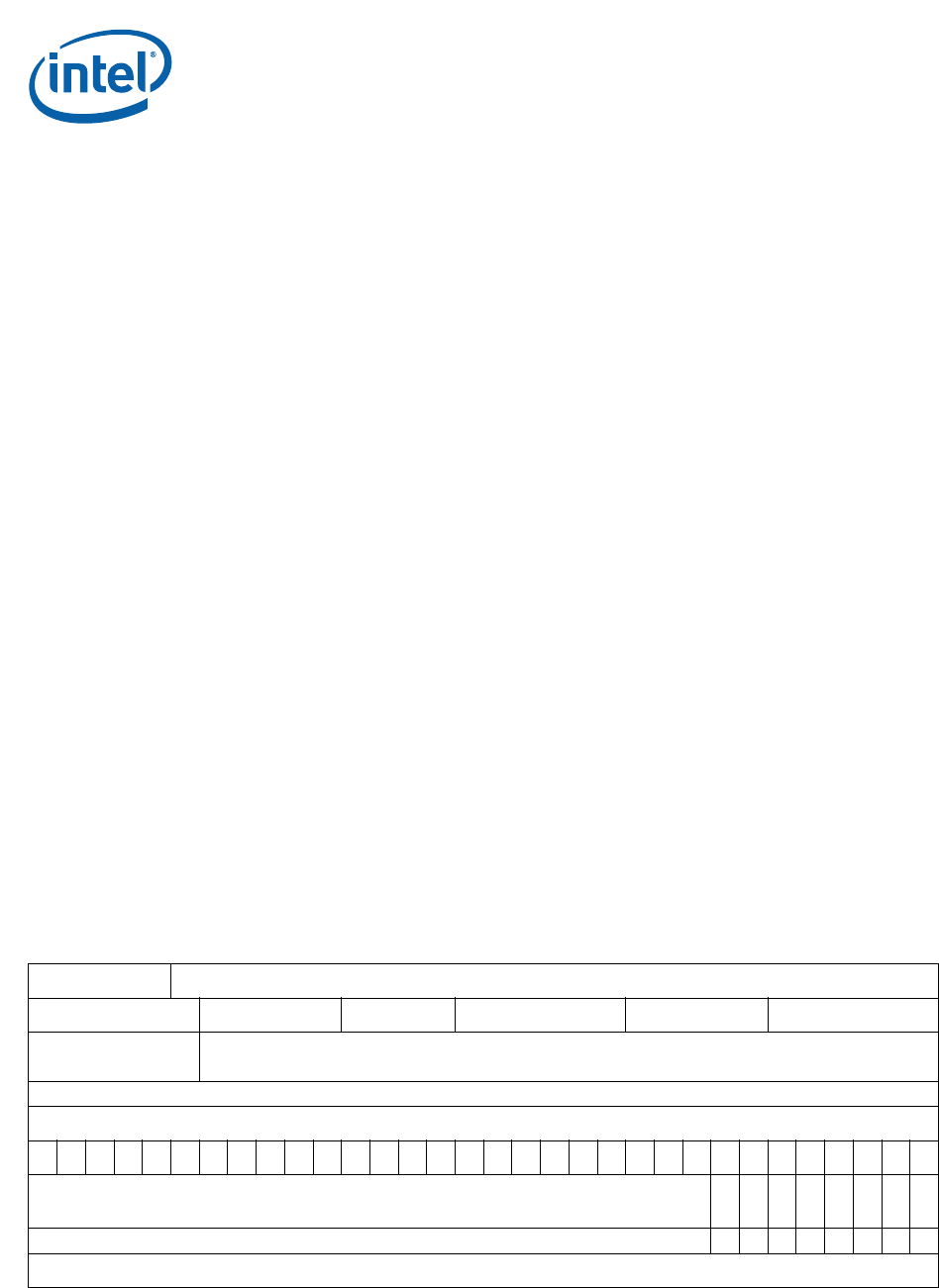

Register Name: UDCCR

Hex Offset Address: 0XC800B000 Reset Hex Value: 0x000000A0

Register

Description:

Universal Serial Bus Device Controller Control Register

Access: Read/Write and Read-Only

Bits

31 876543210

(Reserved)

REM

RSTIR

SRM

SUSIR

RESIR

RSM

UDA

UDE

X 10100000

Resets (Above)