Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 257

PCI Controller—Intel

®

IXP42X product line and IXC1100 control plane processors

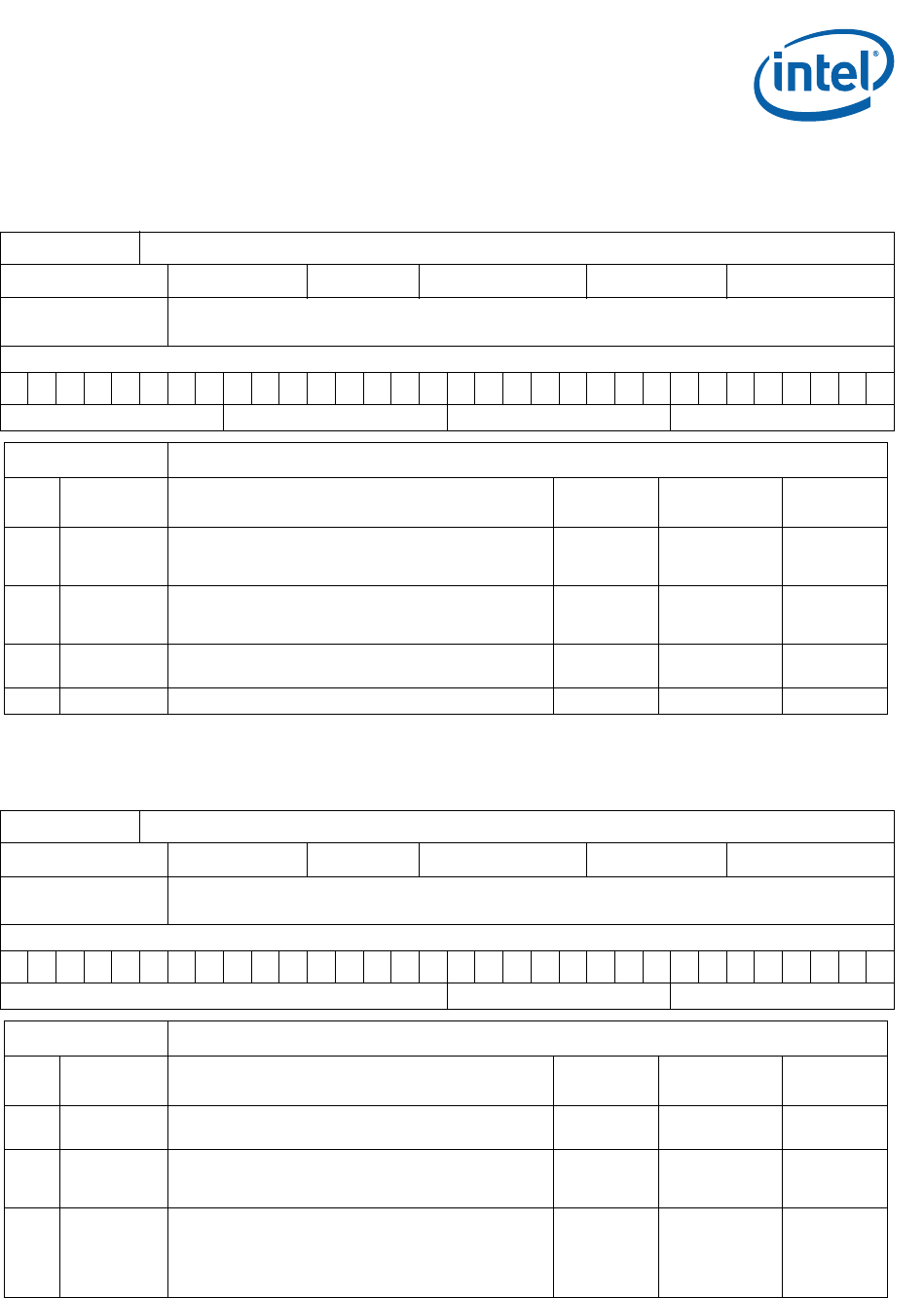

6.14.1.12 Max_Lat, Min_Gnt, Interrupt Pin, and Interrupt Line Register

(PCI_LATINT)

6.14.1.13 Retry Timeout/TRDY Timeout Register

(PCI_RTOTTO)

Register Name: PCI_LATENT

Hex Offset Address: 0x3C Reset Hex Value: 0x00000100

Register

Description:

Miscellaneous register provides Max Latency, Min Grant, Interrupt Pin and Interrupt Line parameters as

specified in the PCI 2.2 Local Bus Specification

Access: See below.

31 24 23 16 15 8 7 0

MaxLat MinGnt IntPin IntLine

Register

PCI_LATENT

Bits Name Description

Reset

Value

PCI Access AHB Access

31:2

4

MaxLat

Indicates how often this device needs access to the

bus, in units of 0.25us. Used by configuration

software to set the value of the Latency Timer.

0x00 RO RW

23:1

6

MinGnt

Indicates the time interval required for a burst

operation, in units of 0.25us. Used by configuration

software to set the value of the Latency Timer.

0x00 RO RW

15:8 IntPin

Indicates which interrupt pin this device connects to.

Set to connect to INT_A#.

0x01 RO RW

7:0 IntLine Indicates interrupt line routing information. 0x00 RW RW

Register Name: PCI_RTOTTO

Hex Offset Address: 0x40 Reset Hex Value: 0x00008080

Register

Description:

Specifies values for the Retry and TRDY timeout timers.

Access: See below.

31 16 15 8 7 0

(Reserved) RetryTO TRDYTO

Register

PCI_RTOTTO

Bits Name Description

Reset

Value

PCI Access AHB Access

31:1

6

(Reserved) 0x00 RO RO

15:8 RetryTO

Specifies value for the Retry timer. Specifies the

maximum number of retries the Master Interface will

accept before terminating the transaction.

0x80 RW RW

7:0 TRDYTO

Specifies value for the TRDY timer. Specifies the

number of PCI clocks the Master Interface will wait

before terminating a transfer with Master Abort when

a target accepts a transaction by asserting DEVSEL#

but does not assert TRDY# or STOP#.

0x80 RW RW