Intel

®

IXP42X product line and IXC1100 control plane processors—PCI Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

270 Order Number: 252480-006US

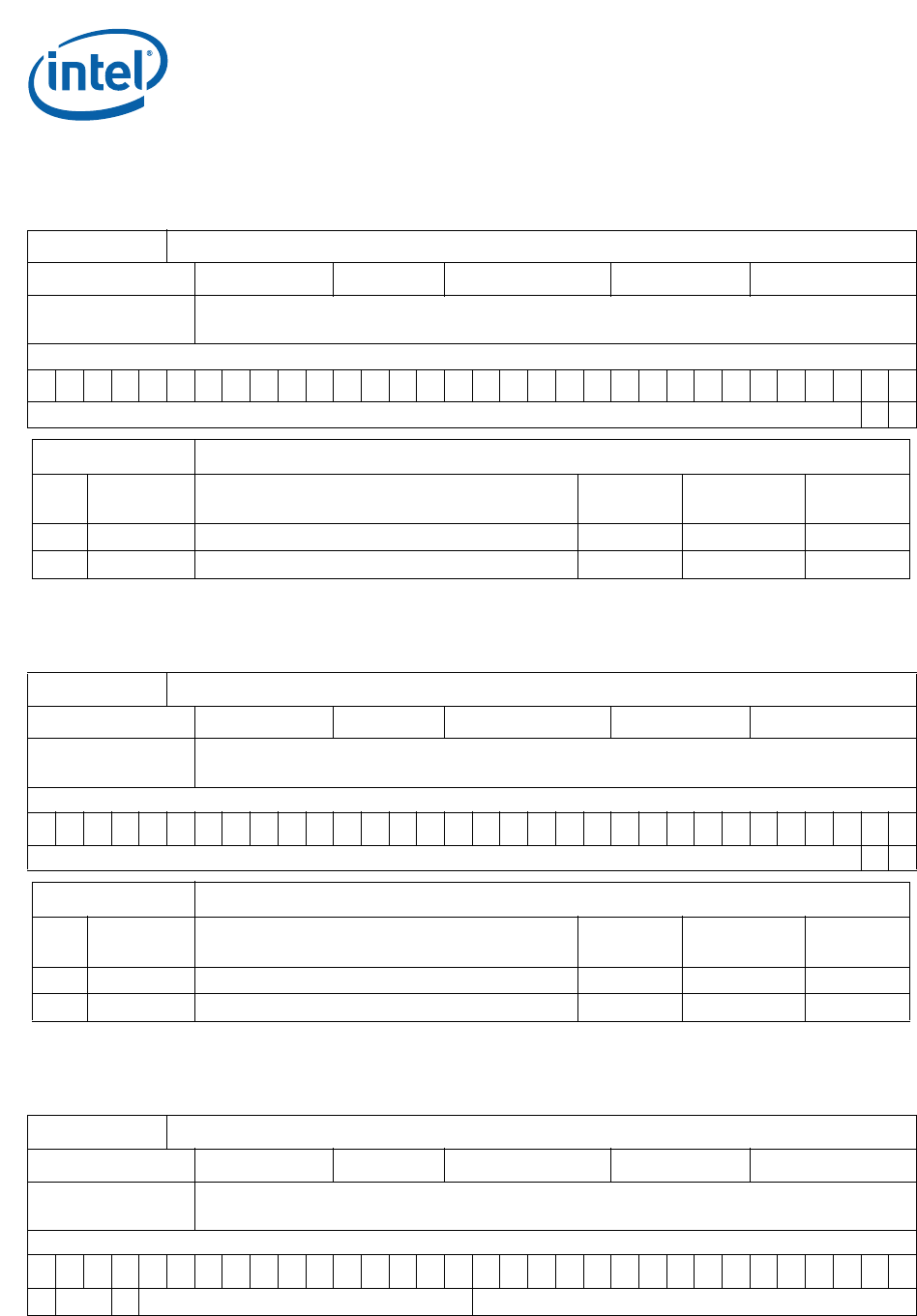

6.14.2.20 AHB to PCI DMA AHB Address Register 1

(PCI_ATPDMA1_AHBADDR)

6.14.2.21 AHB to PCI DMA PCI Address Register 1

(PCI_ATPDMA1_PCIADDR)

6.14.2.22 AHB to PCI DMA Length Register 1

(PCI_ATPDMA1_LENGTH)

Register Name: PCI_ATPDMA1_AHBADDR

Hex Offset Address: 0xC000004C Reset Hex Value: 0x00000000

Register

Description:

Source address on the AHB bus for AHB to PCI DMA transfers. Paired with pci_atpdma0_ahbaddr to allow

buffering of DMA transfer requests.

Access: See below.

31 210

address 0 0

Register

PCI_ATPDMA1_AHBADDR

Bits Name Description

Reset

Value

PCI Access AHB Access

31:2 address AHB word address 0x00000000 RO RW

1:0 Lower AHB address bits hard-wired to zero. 00 RO RO

Register Name: PCI_ATPDMA1_PCIADDR

Hex Offset Address: 0xC0000050 Reset Hex Value: 0x00000000

Register

Description:

Destination address on the PCI bus for AHB to PCI DMA transfers. Paired with pci_atpdma0_pciaddr to

allow buffering of DMA transfer requests.

Access: See below.

31 210

address 0 0

Register

PCI_ATPDMA1_PCIADDR

Bits Name Description

Reset

Value

PCI Access AHB Access

31:2 address PCI word address 0x00000000 RO RW

1:0 Lower PCI address bits hard-wired to zero. 00 RO RO

Register Name: PCI_ATPDMA1_LENGTH

Hex Offset Address: 0xC0000054 Reset Hex Value: 0x00000000

Register

Description:

Provides word count and control for AHB to PCI DMA transfers. Paired with pci_atpdma0_length to allow

buffering of DMA transfer requests.

Access: See below.

31 30 29 28 27 16 15 0

EN

(Rsvd)

BE

(Reserved) wordcount