Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 295

Expansion Bus Controller—Intel

®

IXP42X product line and IXC1100 control plane processors

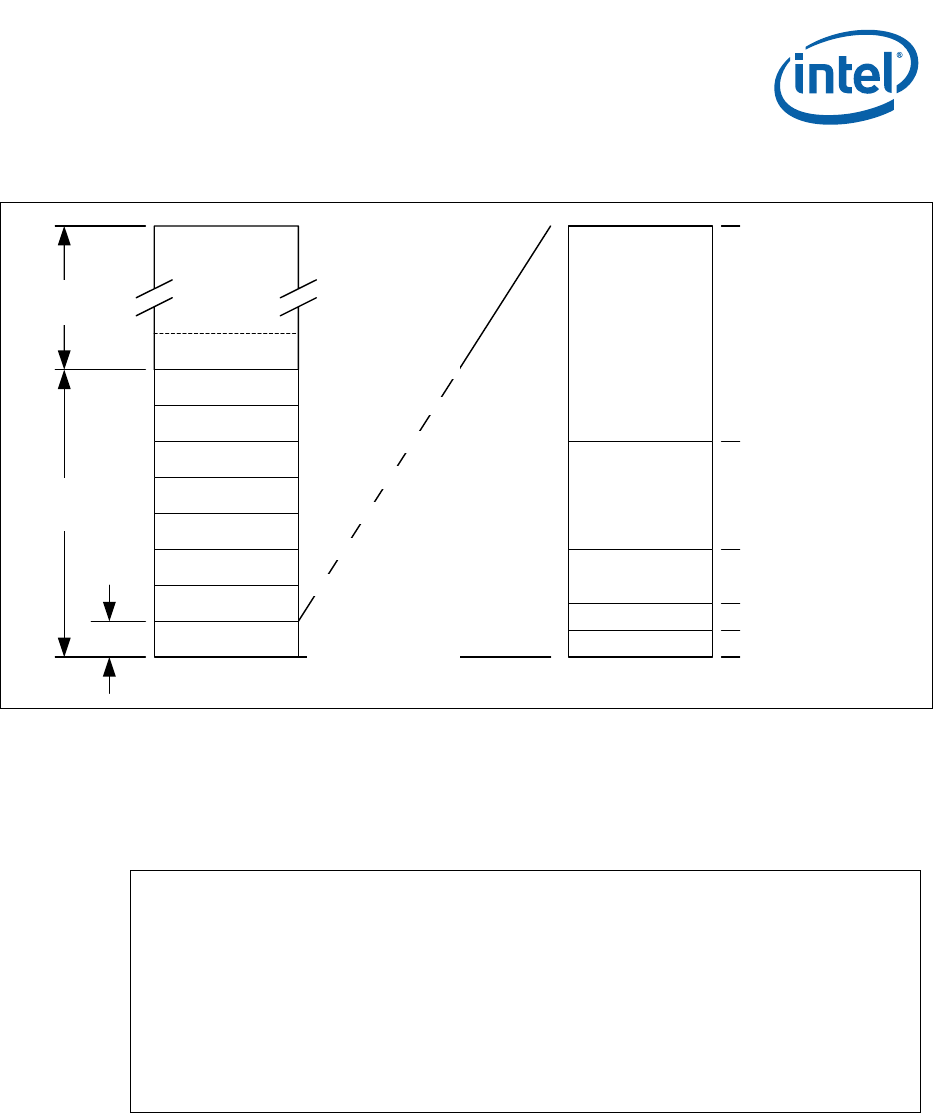

The right side of Figure 58 shows the implementation of bit 13:10 of the each Timing

and Control (EXP_TIMING_CS) Register. A Timing and Control (EXP_TIMING_CS)

Register is implemented for each of the eight chip selects. Each chip select defines a

base region size of 512 bytes with the actual size of the region given by the formula

shown in Figure 59.

8.3 Address and Data Byte Steering

Table 118 shows the address and data mapping from the South AHB to the Expansion

Bus. This table applies to Intel- and Motorola-defined cycles only. Note that — for 32-

bit operations — only read cycles are permissible. Also, for 32-bit read operations to a

byte wide interface. Multiple bytes are collected and then transferred as a complete 32-

bit word. This pattern occurs as shown below for any allowable sub-length read access.

Figure 58. Chip Select Address Allocation

cs_n[7]

128

MBytes

cs_n[0]

cs_n[1]

cs_n[2]

cs_n[3]

cs_n[4]

cs_n[5]

cs_n[6]

base + 0x1000000

base + 0x2000000

base + 0x3000000

base + 0x4000000

base + 0x5000000

base + 0x6000000

base + 0x7000000

base + 0x0000000

16 MB

0b0000 : 512 Bytes

CNFG[3:0] = 0b1111

SIZE = 2

(9 + CNFG)

SIZE = 2

24

SIZE = 16 MBytes

0b1110 : 8 MBytes

0b1101 : 4 MBytes

0b1100 : 2 MBytes

0b1011 : 1 MBytes

SIZE =

2

(9 + CNFG)

cs_n[x]

128

MBytes

cs_n[0] (alias)

.

.

.

base + 0x8000000

base + 0xFFFFFFF

Figure 59. Expansion Bus Memory Sizing

Region Size = 2

(9+CNFG[3:0])

For Examples of how to use this feature:

If bits 13:10 of Timing and Control (EXP_TIMING_CS0) Register 0 = “0000” an

address space of 2

9

= 512 Bytes is defined for chip select 0 (EX_CS0_N).

If bits 13:10 of Timing and Control (EXP_TIMING_CS1) Register 1 = “1000” an

address space of 2

17

= 128KBytes is defined for chip select 1 (EX_CS1_N).

If bits 13:10 of Timing and Control (EXP_TIMING_CS7) Register 7 = “1111” an

address space of 2

24

= 16Mbytes is defined for chip select 7 (EX_CS7_N).