Intel

®

IXP42X product line and IXC1100 control plane processors—PCI Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

264 Order Number: 252480-006US

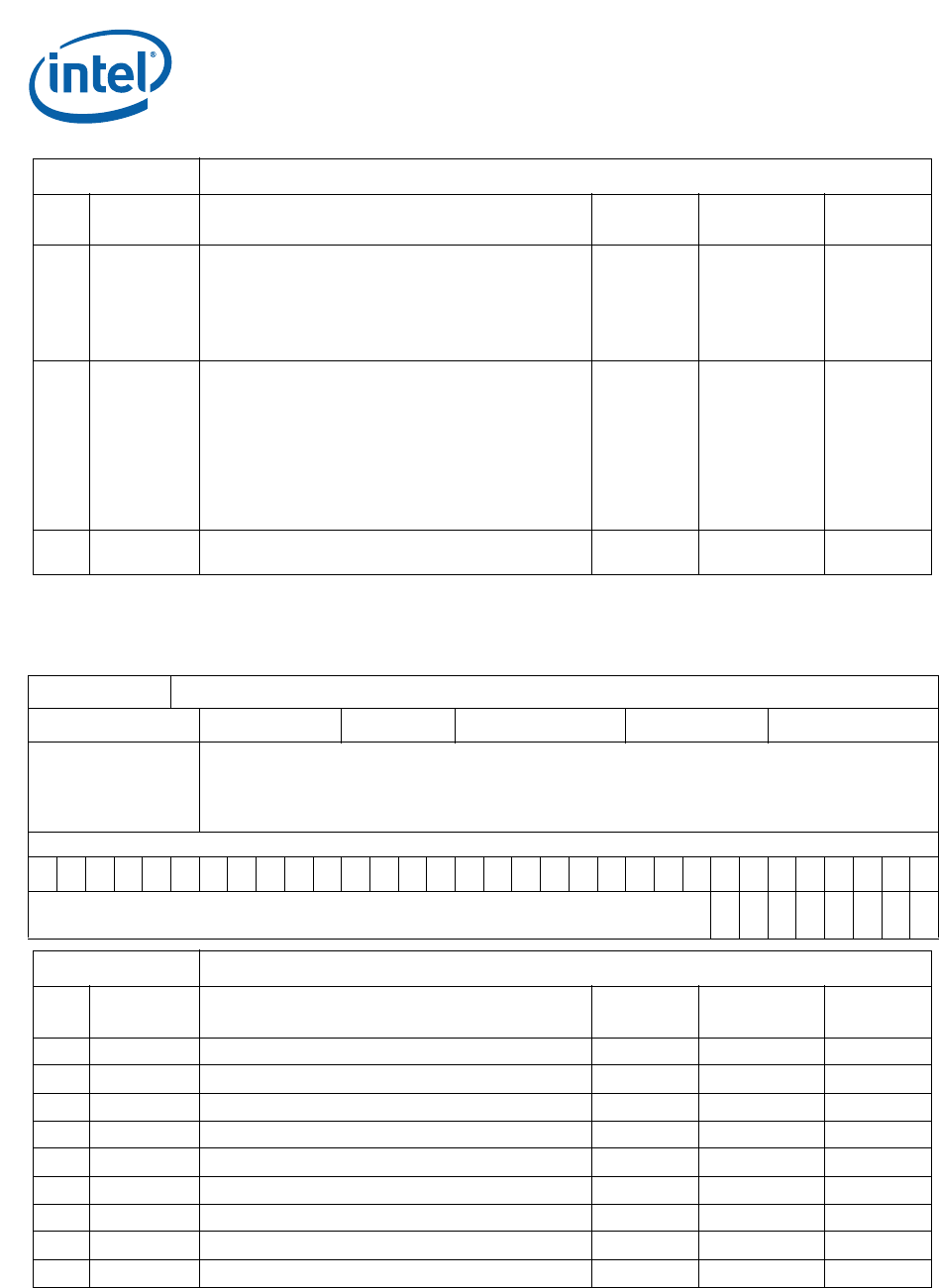

6.14.2.10 PCI Controller Interrupt Enable Register

(PCI_INTEN)

2PPE

PCI Parity Error. Set to a 1 when a parity error occurs

on the PCI bus:

Parity error detected during Master Interface read

cycle.

pad_perr_n (PERR#) asserted by an external target

during a Master write cycle.

0RORW1C

1PFE

PCI Fatal Error. Set to a 1 when one of the following

errors occurs on the PCI bus:

master abort (target did not respond)

target abort

TRDY timeout (external target asserts DEVSEL# but

never asserts TRDY#)

retry timeout (external target issued more retries

than specified by the RetryTO field in the pci_rtotto

register)

0RORW1C

0PSE

PCI System Error. Set to a 1 when the PCI Controller

detects that the PCI SERR# signal has been asserted.

0RORW1C

Register Name: PCI_INTEN

Hex Offset Address: 0xC0000024 Reset Hex Value: 0x00000000

Register

Description:

Interrupt enables for the interrupt status bits in the pci_isr register. Set to a 1 to enable the particular

interrupt. With the exception of PDB (PCI Doorbell), when an interrupt is enabled and the corresponding

bit in the pci_isr register is set, pcc_int will be asserted. If the PDB interrupt is enabled and the

pci_isr.PDB bit is asserted, the PCI_INTA_N output will be asserted to generate an interrupt on the PCI

bus.

Access: See below.

31 876543210

(Reserved)

PDB

ADB

PADC

APDC

AHBE

PPE

PFE

PSE

Register PCI_INTEN

Bits Name Description

Reset

Value

PCI Access AHB Access

31:8 (Reserved) – Read as 0 0x000000 RO RO

7 PDB PCI Doorbell interrupt enable. 0 RO RW

6 ADB AHB Doorbell interrupt enable. 0 RO RW

5 PADC PCI to AHB DMA Complete interrupt enable. 0 RO RW

4 APDC AHB to PCI DMA Complete interrupt enable. 0 RO RW

3 AHBE AHB Error indication interrupt enable. 0 RO RW

2 PPE PCI Parity Error interrupt enable. 0 RO RW

1 PFE PCI Fatal Error interrupt enable. 0 RO RW

0 PSE PCI System Error interrupt enable. 0 RO RW

Register

PCI_ISR (Sheet 2 of 2)

Bits Name Description

Reset

Value

PCI Access AHB Access