Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 133

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

3.7 Performance Monitoring

This section describes the performance monitoring facility of the IXP42X product line

and IXC1100 control plane processors. The events that are monitored can provide

performance information for compiler writers, system application developers and

software programmers.

3.7.1 Overview

The IXP42X product line and IXC1100 control plane processors hardware provide four

32-bit performance counters that allow four unique events to be monitored

simultaneously. In addition, the IXP42X product line and IXC1100 control plane

processors implement a 32-bit clock counter that can be used in conjunction with the

performance counters; its main purpose is to count the number of core clock cycles

which is useful in measuring total execution time.

The IXP42X product line and IXC1100 control plane processors can monitor either

occurrence events or duration events. When counting occurrence events, a counter is

incremented each time a specified event takes place and when measuring duration, a

counter counts the number of processor clocks that occur while a specified condition is

true. If any of the five counters overflow, an interrupt request will occur if it’s enabled.

Each counter has its own interrupt request enable. The counters continue to monitor

events even after an overflow occurs, until disabled by software.

Each of these counters can be programmed to monitor any one of various events.

To further augment performance monitoring, the IXP42X product line and IXC1100

control plane processors clock counter can be used to measure the executing time of an

application. This information combined with a duration event can feedback a

percentage of time the event occurred with respect to overall execution time.

All of the performance monitoring registers are accessible through Coprocessor 14

(CP14). Refer to Table 27 for more details on accessing these registers with MRC and

MCR coprocessor instructions. Access is allowed in privileged mode only. Note that

these registers can’t be access with LDC or STC coprocessor instructions.

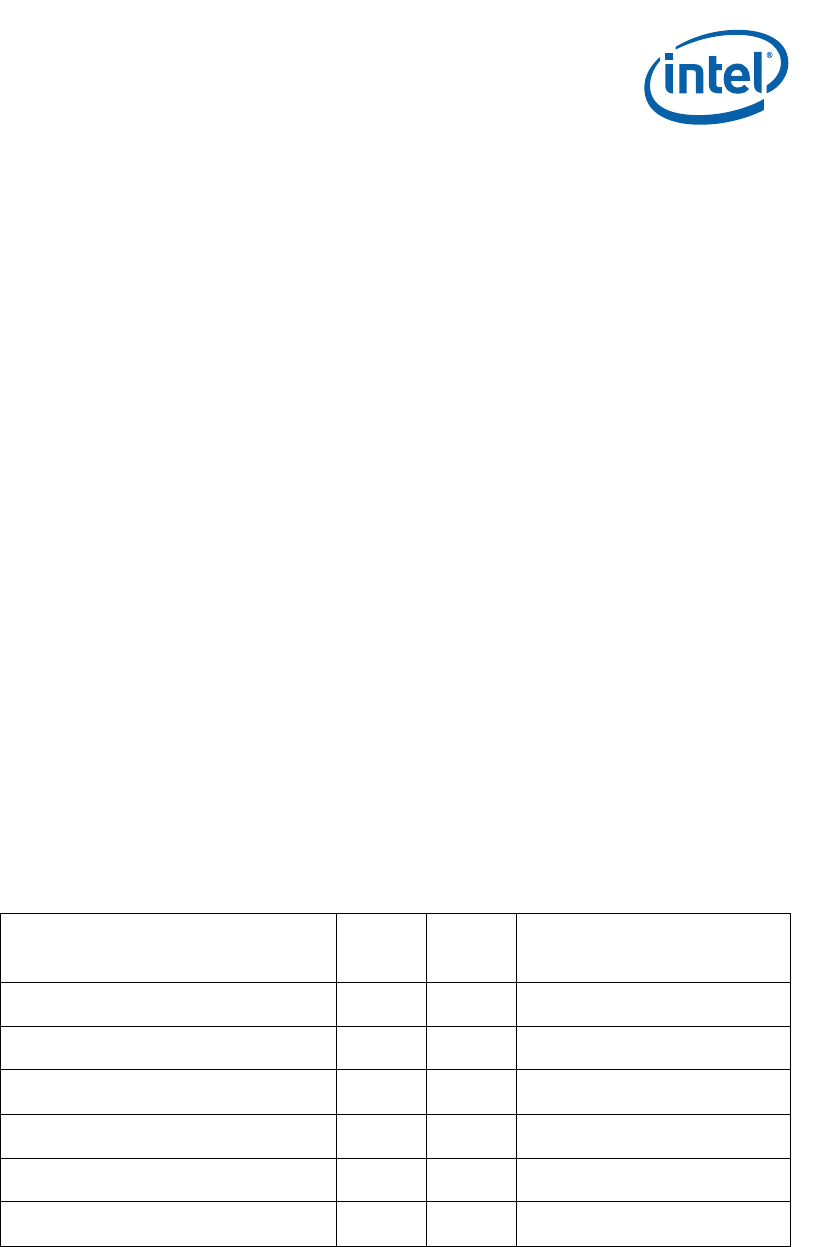

Table 53. Performance Monitoring Registers (Sheet 1 of 2)

Description

CRn

Register

#

CRm

Register

#

Instruction

(PMNC) Performance Monitor Control

Register

0b0000 0b0001

Read: MRC p14, 0, Rd, c0, c1, 0

Write: MCR p14, 0, Rd, c0, c1, 0

(CCNT) Clock Counter Register 0b0001 0b0001

Read: MRC p14, 0, Rd, c1, c1, 0

Write: MCR p14, 0, Rd, c1, c1, 0

(INTEN) Interrupt Enable Register 0b0100 0b0001

Read: MRC p14, 0, Rd, c4, c1, 0

Write: MCR p14, 0, Rd, c4, c1, 0

(FLAG) Overflow Flag Register 0b0101 0b0001

Read: MRC p14, 0, Rd, c5, c1, 0

Write: MCR p14, 0, Rd, c5, c1, 0

(EVTSEL) Event Selection Register 0b1000 0b0001

Read: MRC p14, 0, Rd, c8, c1, 0

Write: MCR p14, 0, Rd, c8, c1, 0

(PMN0) Performance Count Register 0 0b0000 0b0010

Read: MRC p14, 0, Rd, c0, c2, 0

Write: MCR p14, 0, Rd, c0, c2, 0