Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 415

Timers—Intel

®

IXP42X product line and IXC1100 control plane processors

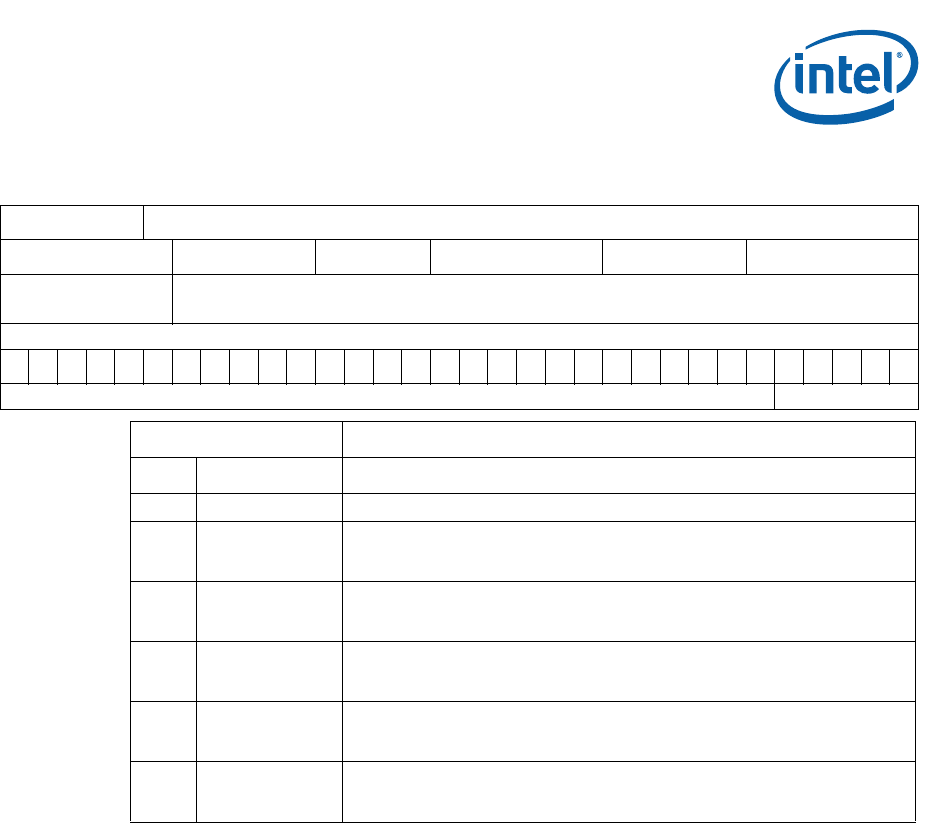

14.4.9 Timer Status

§ §

Register Name: OST_STATUS

Hex Offset Address: 0x C800 5020 Reset Hex Value: 0x00000000

Register

Description:

Timer Status Register

Access: Read/Bit Clear.

31 54 0

(Reserved) ost status bits

Register

OST_STATUS

Bits Name Description

31:5 (Reserved). Returns 0 if read

4warm_reset

Logic 1 if a warm reset has occurred. A warm reset is when the watch-dog

timer caused the reset to occur. Writing logic 1 to this bit will clear the bit if the

bit is set.

3 Ost_wdog_int_val

Logic 1 when a watch-dog timer’s interrupt has occurred and the watch-dog

timer interrupt enable bit is set. Writing logic 1 to this bit will clear the bit when

the condition that caused the bit to be set is no longer present.

2 Ost_ts_int_val

Logic 1 when the time-stamp timer reaches the maximum count value. Writing

logic 1 to this bit will clear the bit when the condition that caused the bit to be

set is no longer present.

1 Ost_tim1_int_val

Logic 1 when the general-purpose timer’s down counter has reached a value of

zero. Writing logic 1 to this bit will clear the bit when the condition that caused

the bit to be set is no longer present.

0 Ost_tim0_int_val

Logic 1 when the general-purpose timer’s down counter has reached a value of

zero. Writing logic 1 to this bit will clear the bit when the condition that caused

the bit to be set is no longer present.