Intel

®

IXP42X product line and IXC1100 control plane processors—Universal Serial Bus (USB)

v1.1 Device Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

518 Order Number: 252480-006US

18.5.20 UDC Status/Interrupt Register 0 (UISR0)

The UDC status/interrupt registers (USIR0 and USIR1) contain bits that are used to

generate the UDC’s interrupt request. Each bit in the UDC status/interrupt registers is

logically ORed together to produce one interrupt request.

When the ISR for the UDC is executed, it must read the UDC status/interrupt register

to determine why the interrupt occurred.

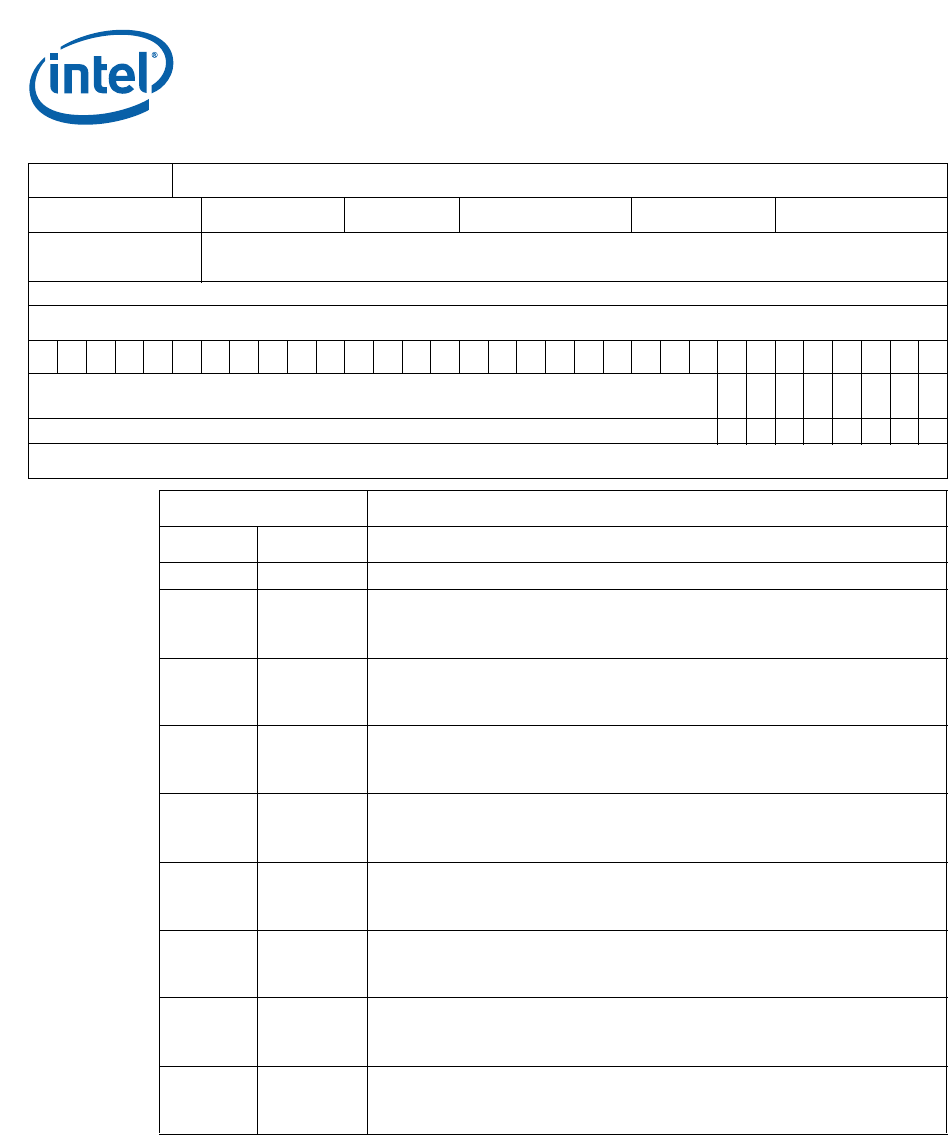

Register Name: UICR1

Hex Offset Address: 0 x C800B054 Reset Hex Value: 0x000000FF

Register

Description:

Universal Serial Bus Device Controller Interrupt Control Register 1

Access: Read/Write

Bits

31 876543210

(Reserved)

IM15

IM14

IM13

IM12

IM11

IM10

IM9

IM8

11111111

Resets (Above)

Register

UICR1

Bits Name Description

31:8 Reserved for future use.

7IM15

Interrupt mask for Endpoint 15.

0 = Transmit interrupt enabled.

1= Transmit interrupt disabled.

6IM14

Interrupt mask for Endpoint 14.

0 = Receive interrupt enabled.

1 = Receive interrupt disabled.

5IM13

Interrupt mask for Endpoint 13.

0 = Transmit interrupt enabled.

1 = Transmit interrupt disabled.

4IM12

Interrupt mask for Endpoint 12.

0 = Receive interrupt enabled.

1 = Receive interrupt disabled.

3IM11

Interrupt mask for Endpoint 11.

0 = Transmit interrupt enabled.

1 = Transmit interrupt disabled.

2IM10

Interrupt mask for Endpoint 10.

0 = Receive interrupt enabled.

1 = Receive interrupt disabled.

1IM9

Interrupt mask for Endpoint 9.

0 = Receive interrupt enabled.

1 = Receive interrupt disabled.

0IM8

Interrupt Mask for Endpoint 8.

0 = Transmit interrupt enabled.

1 = Transmit interrupt disabled.