Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 23

—Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

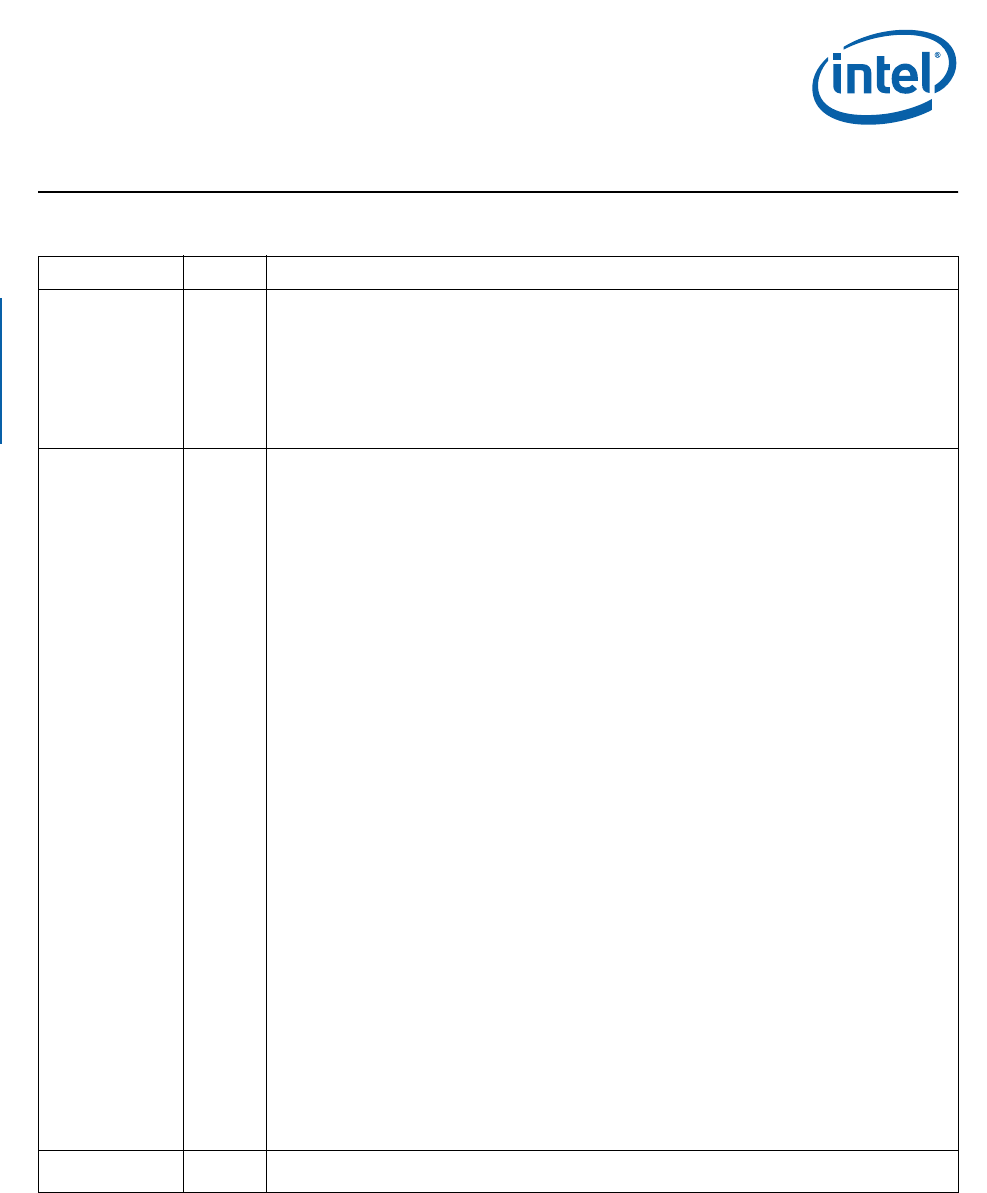

Revision History

Date Revision Description

September 2006 006

1. Added the 533MHz IXP423 to Figure 2

2. Updated Table 3.1.1.1, Table 3.8.2.1, and the note for Table 126

3. Updated Section 12.1

4. Added clarifying information regarding the MDI Interface to Section 15.1.3,

Section 15.2.46, and Table 153

5. Added additional description information to bit 3 of Table 124

6. Updated Table 96, “Memory Map”

Incorporated specification changes, specification clarifications and document changes from the

Intel

®

IXP4XX Product Line Specification Update (306428-004 and 306428-005)

March 2005 005

Incorporated specification changes, specification clarifications and document changes from the

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

Specification Update (252702-006).

1. Removed Table 1, “Processor Features”. Refer to the Intel

®

IXP42X Product Line of

Network Processors and IXC1100 Control Plane Processor Datasheet.

2. Replaced Figure 1, Figure 2, Figure 3, Figure 4, and Figure 5. Added new product

IXP423, Figure 2.

3. Updated Table 2, “Network Processor Functions”.

4. Added Section 2.12, “Universal Asynchronous Receiver Transceiver”

5. Updated note on Section 3.1.1.1, “Page (P) Attribute Bit”.

6. Updated Table 94, “Network Processor Functions”.

7. Added Implication to Section 6.1, “PCI Controller Configured as Host”.

8. Added Section 6.6.1, “PCI Byte Enables”.

9. Corrected Register table bit 15, Section 6.14.2.8, “PCI Controller Control and Status

Register”.

10. Corrected Figure 60, “Expansion Bus Peripheral Connection“.

11. Replaced all figures in the Expansion Bus Controller chapter (Figure 63–Figure 76).

12. Corrected register table bits 20:17, Section 8.9.9, “Configuration Register 0”.

13. Corrected Table 125, “Intel XScale® Processor Speed Expansion Bus Configuration

Strappings”.

14. Added new Table 127, “Simulated Expansion Bus Performance”.

15. Updated Table 151, “Processors’ Devices with Ethernet Interface”.

16. Updated Figure 80, “Multiple Ethernet PHYS Connected to Processor“.

17. Enhanced Deferral Parameter Registers information in Section 15.1.4, “Transmitting

Ethernet Frames with MII Interfaces”.

18. Enhanced information regarding Dropped Broadcast Frames in Section 15.1.5,

“Receiving Ethernet Frames with MII Interfaces”.

19. Corrected register description in Section 15.2, “Register Descriptions”.

20. Corrected register description in Section 15.2.1, “Transmit Control 1”.

21. Corrected register description in Section 15.2.2, “Transmit Control 2”.

22. Corrected register description and added notes to Section 15.2.3, “Receive Control 1”.

23. Corrected register description in Section 15.2.4, “Receive Control 2”.

24. Corrected register description in Section 15.2.9, “Transmit Deferral Parameters”.

25. Corrected register description in Section 15.2.10, “Receive Deferral Parameters”.

26. Corrected register description in Section 15.2.11, “Transmit Two Part Deferral

Parameters 1”.

27. Corrected register description in

Section 15.2.12, “Transmit Two Part Deferral

Parameters 2”.

28. Corrected register description in Section 15.2.46, “Core Control”.

29. Updated Table 152, “Processors’ with Ethernet Interface”.

30. Updated Table 154, “Processors with HSS”.

31. Updated Table 173, “Processors’ Devices with UTOPIA”.

Change bars indicate areas of change.

June 2004 004

Updated Intel

®

product branding. Change bars were retained from the previous release of this

document (003).