Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

108 Order Number: 252480-006US

3.6.11.6.3 DBG.RR

The debugger uses DBG.RR as part of the synchronization that occurs between the

debugger and debug handler for accessing RX. This bit contains the value of

TXRXCTRL[31] after a Capture_DR. The debug handler automatically sets

TXRXCTRL[31] by doing a write to RX.

The debugger polls DBG.RR to determine when the handler has read the previous data

from RX.

The debugger sets TXRXCTRL[31] by setting the DBG.V bit.

3.6.11.6.4 DBG.V

The debugger sets this bit to indicate the data scanned into DBG_SR[34:3] is valid data

to write to RX. DBG.V is an input to the RX Write Logic and is also cleared by the RX

Write Logic.

When this bit is set, the data scanned into the DBG_SR will be written to RX following

an Update_DR. If DBG.V is not set and the debugger does an Update_DR, RX will be

unchanged.

This bit does not affect the actions of DBG.FLUSH or DBG.D.

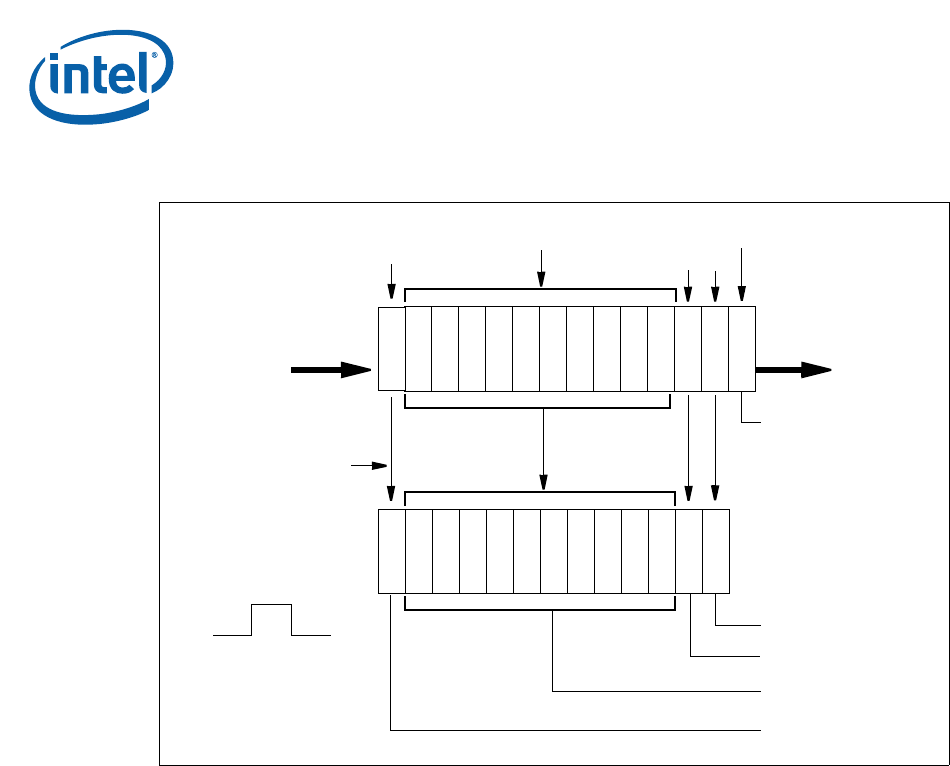

Figure 20. DBGRX Data Register

12

3334

TDO

TDI

DBG_SR

Capture_DR

Update_DR

DBG_REG

1

2334

35

TCK

0

0

RX TXRXCTRL[31]

DBG.RR

DBG.FLUSH

DBG.RX

DBG.V

0

0

1

DBG.D

cleared by

RX Write Logic