Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 391

General Purpose Input/Output (GPIO)—Intel

®

IXP42X product line and IXC1100 control plane

processors

† When the value of the GPIO frequency terminal count is set to 0xF and the value of the GPIO duty cycle

terminal count is set to 0xF, the associated GPIO (GPIO 14 or GPIO 15) will output a clock of 33 MHz

with a 50% duty cycle.

There is one special condition defined for the output clock on GPIO 14 and GPIO 15.

When the GPIO Frequency Terminal Count = F and the GPIO Duty Cycle Terminal Count

= F, the output of the clock generator block will be 33.33 MHz with a 50% duty cycle. If

the GPIO Duty Cycle Terminal Count is programmed to be greater than or equal to the

GPIO Frequency Terminal Count (TC), the clock generator will output logic 1. The

General-Purpose Clock Control Register is set to a hexadecimal value of 0x01100000

after receiving a reset.

12.4 Register Description

12.4.1 GPIO Output Register

(GPOUTR)

Each pin’s output data is controlled by programming this register. Each of the 16 bits in

the register represents the data to be put on the output through a tristate buffer,

depending upon the status of the GPOER.

210 ns 1 1 0 1 1 1 0 1

225 ns 1 1 1 0 1 1 1 0

240 ns

†

11111111

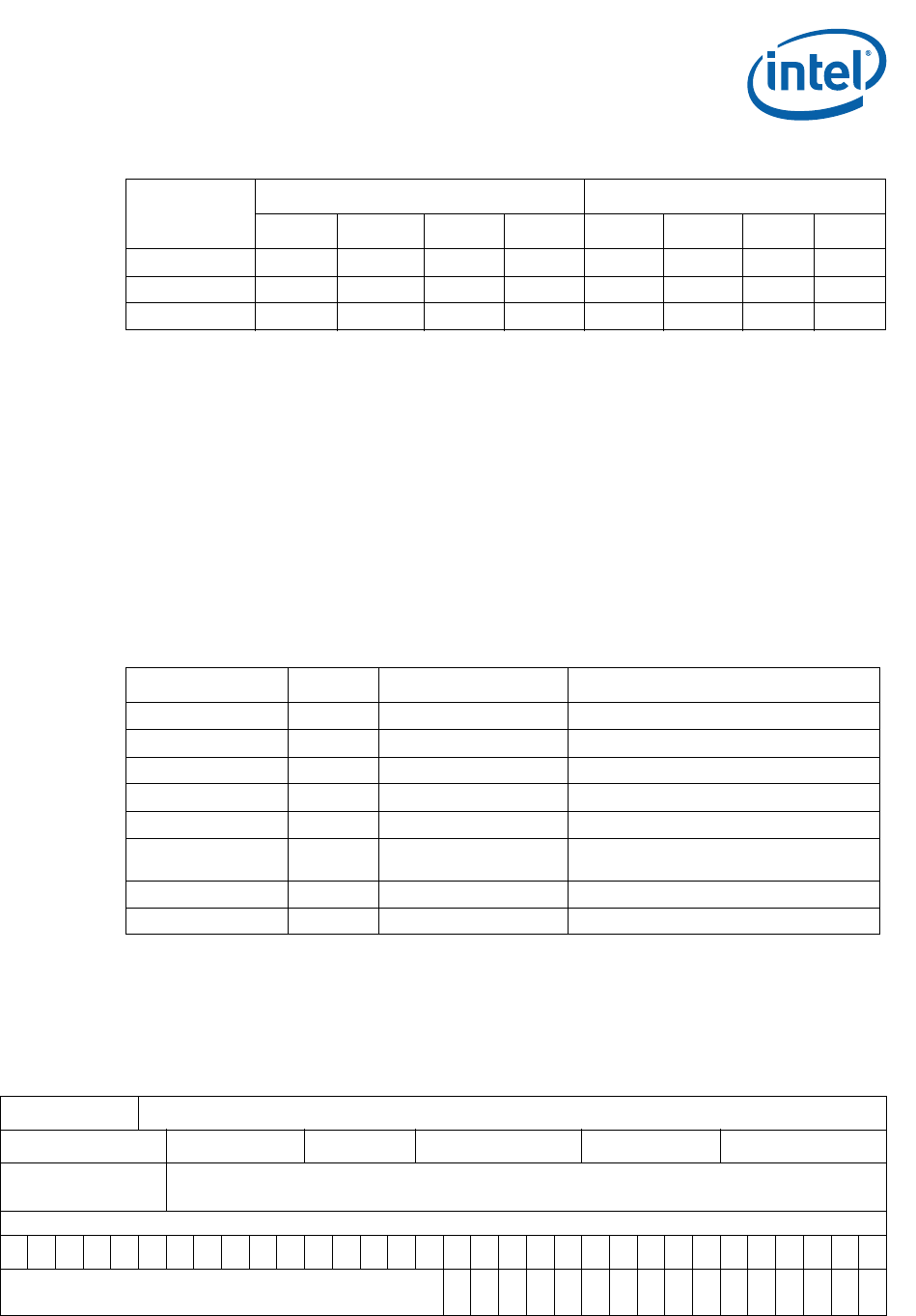

Table 147. GPIO Duty Cycle Select (Sheet 2 of 2)

Duty Cycle

(Low Time)

GPIO15 – Duty Cycle Terminal Count GPIO14 – Duty Cycle Terminal Count

Bit 19 Bit 18 Bit 17 Bit 16 Bit 3 Bit 2 Bit 1 Bit 0

Table 148. GPIO Registers Overview

Address R/W Name Description

0xC8004000 R/W GPOUTR GPIO pin data output register.

0xC8004004 R/W GPOER GPIO pin out enable register.

0xC8004008 R GPINR GPIO pin status register.

0xC800400C R/W GPISR GPIO interrupt status register.

0xC8004010 R/W GPIT1R GPIO interrupt type register, inputs 7:0

0xC8004014 R/W GPIT2R

GPIO pin interrupt type register, inputs

15:8

0xC8004018 R/W GPCLKR GPIO Clock Control Register

0xC800401C RO Reserved Reserved

Register Name: GPOUTR

Hex Offset Address: 0xC800 4000 Reset Hex Value: 0x00000000

Register

Description:

I/O Output register. Controls output value of GPIO pins, depending on tristate control from GPOER.

Access: Read/Write.

31 161514131211109876543210

(Reserved)

DO15

DO14

DO13

DO12

DO11

DO10

DO9

DO8

DO7

DO6

DO5

DO4

DO3

DO2

DO1

DO0