Intel

®

IXP42X product line and IXC1100 control plane processors—SDRAM Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

284 Order Number: 252480-006US

A page hit is valid if the memory location falls within the location as specified by the

open page register:

If the RAS address for the current SDRAM access matches that stored within a valid

page registers, then there is a page hit. When the current transaction hits an open

page, then the page is already active. The read or write command may be issued

without a row-activate command. It is important to note that when the refresh timer

expires, the SDRAM Controller will issue a precharge command, which closes all pages,

followed by the issue of an auto-refresh command.

When the current transaction misses, the open page (maintained by the page

registers) is selected then the SDRAM controller closes the open page pointed to by

issuing a precharge command. The SDRAM controller then opens the correct page with

a row-activate command and the SDRAM Controller completes the requested

transaction with a read or a write command. When the SDRAM Controller opens the

new page, the RAS address is stored in the page address register. This new value

stored in the page register may be used to compare for future transaction page hit/

misses.

The SDRAM controller interfaces to the AHB as a non-splitting bus slave. In so doing

this, the SDRAM Controller follows a certain set of rules during any access. These rules

can be helpful in understanding the performance and capability of the overall chip

performance.

• The South AHB that host the Intel XScale processor will be the only master capable

of writing to the configuration register of the SDRAM.

• AHBs will access the SDRAM in a pipe-lined fashion (bus accesses will be pipe-lined

together whenever possible).

• The SDRAM controller will insert wait states back to an AHB Master if the SDRAM

Controller is currently involved in an SDRAM transaction from the other AHB.

• If both AHB interfaces try to access the SDRAM at the same time (two transactions

occur at the same time on both buses to access the SDRAM controller), the South

AHB bus that host the Intel XScale processor will have priority.

• Transfers on both AHBs have a maximum of eight words and will be word aligned.

• Data transfers on both AHBs support data size listed in the Table 112 but will be

word aligned. Therefore, the DQM(3:0) signals going to the SDRAM will always be

0x0, 0x1, 0x2, 0x3, 0x4, 0x6, 0x8, or 0xC. Any other values on DQM(3:0) will be

unachievable.

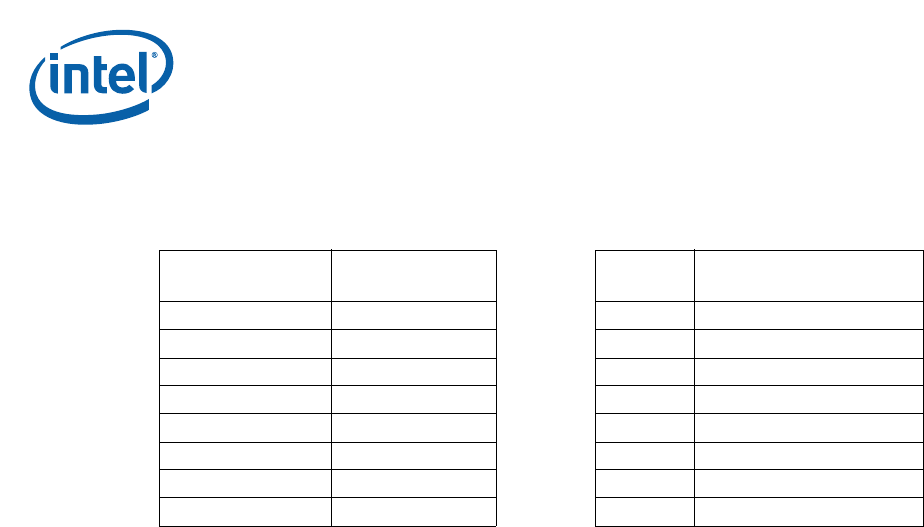

Table 111. Page Register Allocation

SDM_CS_N[1:0]

(Physical Bank)

SDM_BA[1:0]

(Internal Bank)

Valid bit

Page Registers

(13 bits)

Bank 0 Leaf 0 RAS address 0

Bank 0 Leaf 1 RAS address 1

Bank 0 Leaf 2 RAS address 2

Bank 0 Leaf 3 RAS address 3

Bank 1 Leaf 0 RAS address 4

Bank 1 Leaf 1 RAS address 5

Bank 1 Leaf 2 RAS address 6

Bank 1 Leaf 3 RAS address 7