Intel

®

IXP42X product line and IXC1100 control plane processors—AHB Queue Manager (AQM)

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

566 Order Number: 252480-006US

21.5.7 Queue Interrupt Enable Register 0 – 1

21.5.8 Queue Interrupt Register 0 – 1

There are two interrupt registers corresponding respectively to the two AQM interrupts,

aqm_int[0] and aqm_int[1]. Queue Interrupt register 0 represents queues 0-31, while

register 1 represents queues 32-63. Following an interrupt, the appropriate register

can be read to determine which queue or queues caused the interrupt. Any bit in the

interrupt register can be cleared via writing a one to the appropriate bit position.

Writing a’1’ to a bit in the Interrupt register will provide a reset only operation for that

bit. Clearing all set bits (by writing ‘1’s in those locations) in the Interrupt Register will

remove the interrupt (de-assert). The interrupt cannot be generated again by the same

source, until the active status flag condition is removed and then reasserted again. The

bit INT0SRCSELREG0 in the INT0SRCSELREG0 register changes the operation of the

interrupt from a rising edge sensitive operation to a level sensitive one.

21.5.9 Queue Configuration Words 0 - 63

The 64 queue configuration words are located in internal SRAM and require initialization

prior to AQM usage. The read and write pointers need to be cleared on initialization,

since this reflects an empty queue. A system reset sets the status registers to reflect

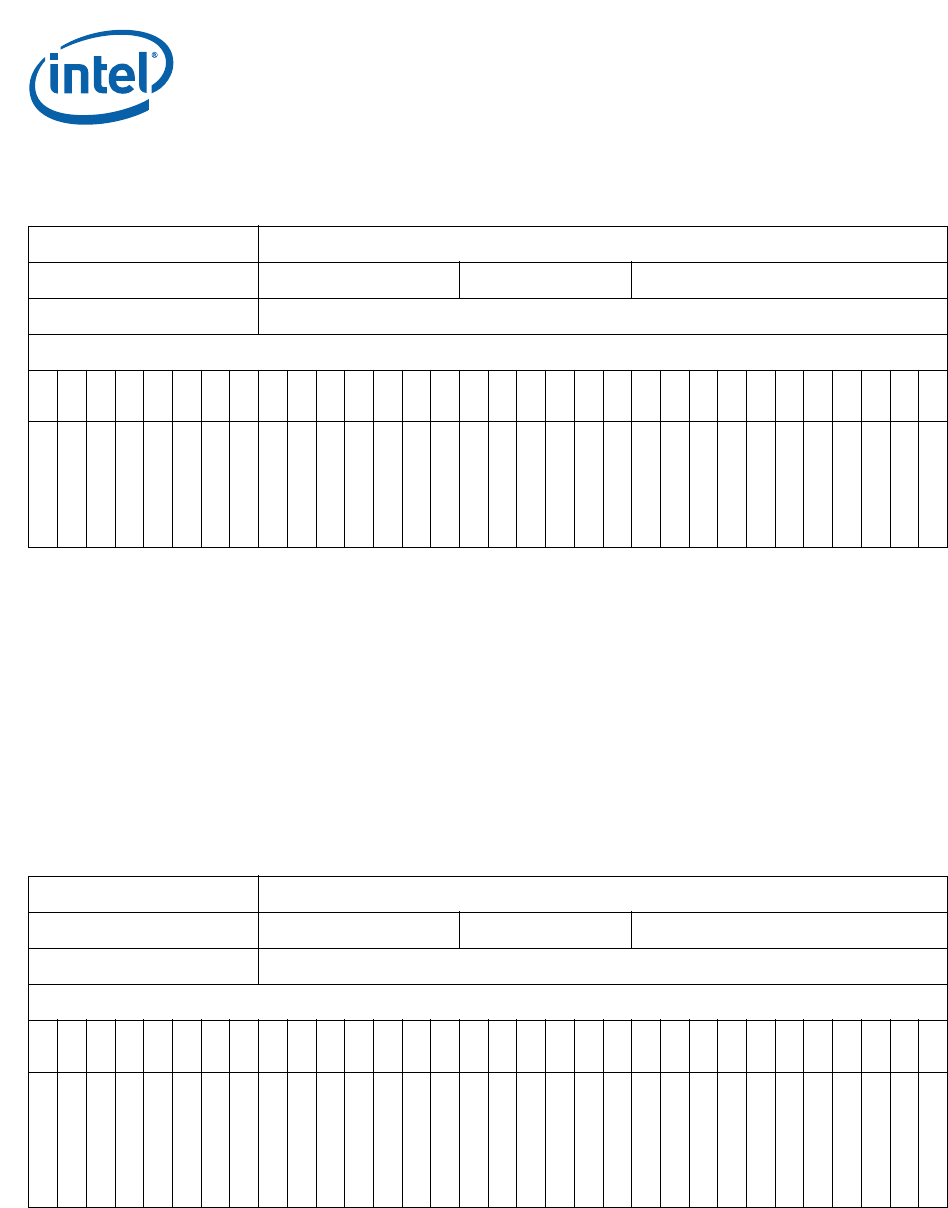

Register Name: QUEIEREG(0 <= n <=1)

Physical Address:

Reg #n 0x(0430 + 4n)

Reset Hex Value: 0x00000000

Register Description: Interrupt enables for the queues 0-63. IE: ‘1’ – Enable

Access: Read/Write

3

1

2

4

2

3

1

6

1

5

87 0

Q(32n + 31) IE

Q(32n + 30) IE

Q(32n + 29) IE

Q(32n + 28) IE

Q(32n + 27) IE

Q(32n + 26) IE

Q(32n + 25) IE

Q(32n + 24) IE

Q(32n + 23) IE

Q(32n + 22) IE

Q(32n + 21) IE

Q(32n + 20) IE

Q(32n + 19) IE

Q(32n + 18) IE

Q(32n + 17) IE

Q(32n + 16) IE

Q(32n + 15) IE

Q(32n + 14) IE

Q(32n + 13) IE

Q(32n + 12) IE

Q(32n + 11) IE

Q(32n + 10) IE

Q(32n + 9) IE

Q(32n + 8) IE

Q(32n + 7) IE

Q(32n + 6) IE

Q(32n + 5) IE

Q(32n + 4) IE

Q(32n + 3) IE

Q(32n + 2) IE

Q(32n + 1) IE

Q(32n) IE

Register Name: QUEINTREG(0 <= n <=1)

Physical Address:

Reg #n 0x(0438 + 4n)

Reset Hex Value: 0x00000000

Register Description: Interrupt Register for the 64 queues. INT: ‘1’ – interrupt occurred

Access: Read/Write to Reset

3

1

2

4

2

3

1

6

1

5

87 0

Q(32n + 31) INT

Q(32n + 30) INT

Q(32n + 29) INT

Q(32n + 28) INT

Q(32n + 27) INT

Q(32n + 26) INT

Q(32n + 25) INT

Q(32n + 24) INT

Q(32n + 23) INT

Q(32n + 22) INT

Q(32n + 21) INT

Q(32n + 20) INT

Q(32n + 19) INT

Q(32n + 18) INT

Q(32n + 17) INT

Q(32n + 16) INT

Q(32n + 15) INT

Q(32n + 14) INT

Q(32n + 13) INT

Q(32n + 12) INT

Q(32n + 11) INT

Q(32n + 10) INT

Q(32n + 9) INT

Q(32n + 8) INT

Q(32n + 7) INT

Q(32n + 6) INT

Q(32n + 5) INT

Q(32n + 4) INT

Q(32n + 3) INT

Q(32n + 2) INT

Q(32n + 1) INT

Q(32n) INT