Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 353

Universal Asynchronous Receiver Transceiver (UART)—Intel

®

IXP42X product line and IXC1100

control plane processors

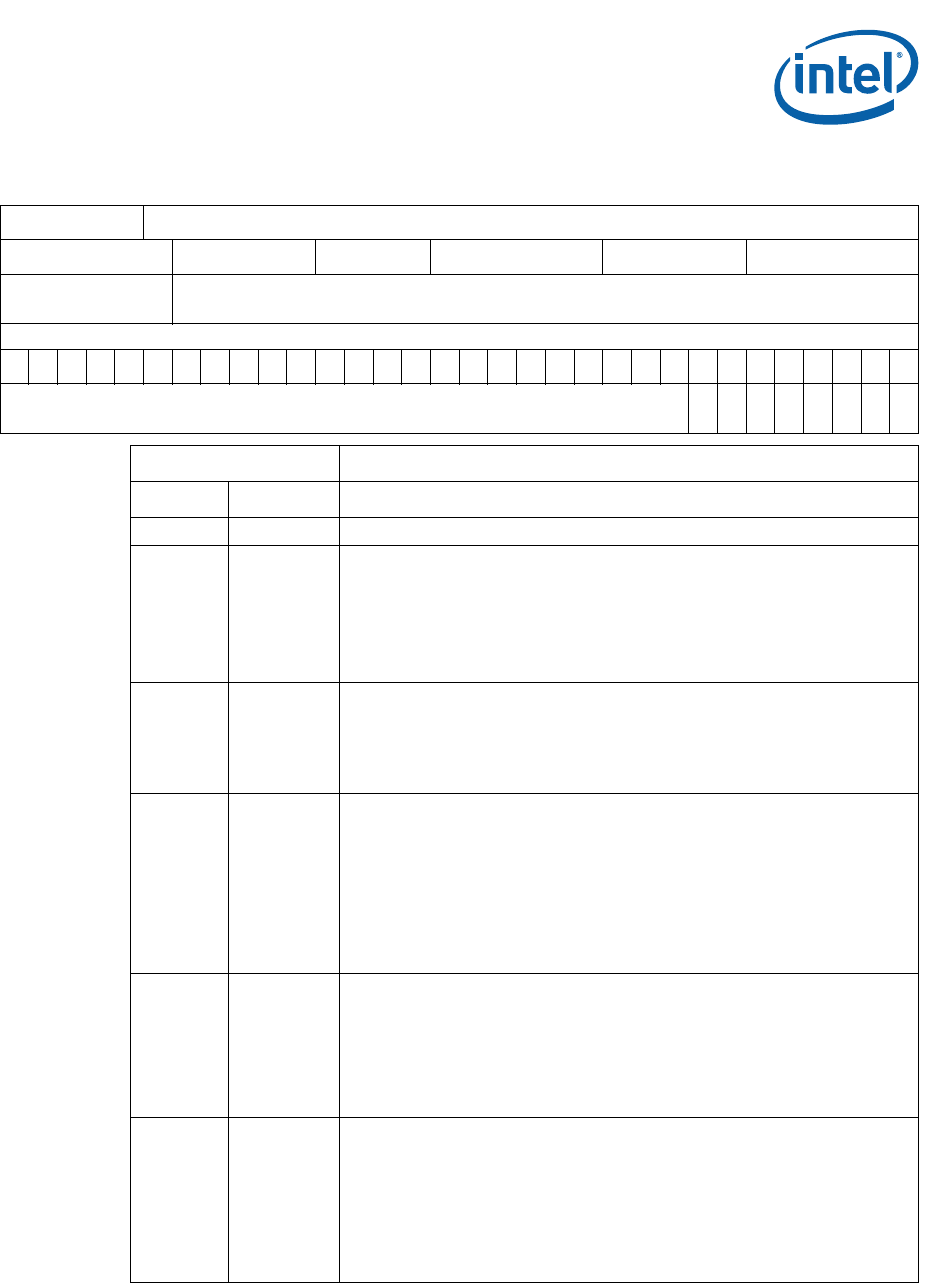

10.4.10 Line Status Register

Register Name: LSR

Hex Offset Address: 0xC800 0014 Reset Hex Value: 0x00000060

Register

Description:

Line Status Register

Access: Read Only.

31 876543210

(Reserved)

FIFOE

TEMT

TDRQ

BI FE

PE

OE

DR

Register LSR (Sheet 1 of 2)

Bits Name Description

31:8 (Reserved)

7FIFOE

FIFO Error Status: In non-FIFO mode, this bit is 0. In FIFO Mode, FIFOE is set

to 1 when there is at least a parity error, framing error, or break indication for

any of the characters in the FIFO.

Note that a processor read to the Line Status register does not reset this bit.

FIFOE is reset when all error bytes have been read from the FIFO.

0 = Non-FIFO mode or no errors in receiver FIFO

1 = At least one character in receiver FIFO has errors

6TEMT

Transmitter Empty: TEMT is set to a logic 1 when the Transmit Holding

register and the Transmitter Shift register are both empty. It is reset to logic 0

when either the Transmit Holding register or the transmitter shift register

contains a data character.

In FIFO mode, TEMT is set to 1 when the transmitter FIFO and the Transmit

Shift register are both empty.

5TDRQ

Transmit Data Request: TDRQ indicates that the UART is ready to accept a

new character for transmission.

In Non-FIFO mode, The TDRQ bit is set to logic 1 when a character is

transferred from the Transmit Holding register into the Transmit Shift register.

The bit is reset to logic 0 concurrently with the loading of the Transmit Holding

register by the processor.

In FIFO mode, TDRQ is set to 1 when half of the characters in the FIFO have

been loaded into the Shift register or the RESETTF bit in FCR has been set to 1.

It is cleared when the FIFO has more than half data. If more than 64 characters

are loaded into the FIFO, the excess characters are lost.

4BI

Break Interrupt: BI is set to a logic 1 when the received data input is held in

the spacing (logic 0) state for longer than a full word transmission time (that is,

the total time of Start bit + data bits + parity bit + stop bits). The Break

indicator is reset when the processor reads the Line Status Register.

In FIFO mode, only one character (equal to 00H) is loaded into the FIFO

regardless of the length of the break condition. BI shows the break condition for

the character at the bottom of the FIFO, not the most recently received

character.

3FE

Framing Error: FE indicates that the received character did not have a valid

stop bit. FE is set to a logic 1 when the bit following the last data bit or parity bit

is detected as a logic 0 bit (spacing level). The FE indicator is reset when the

processor reads the Line Status Register.

The UART will resynchronize after a framing error. To do this, it assumes that

the framing error was due to the next start bit, so it samples this “start” bit

twice and then takes in the “data”.

In FIFO mode, FE shows a framing error for the character at the bottom of the

FIFO, not for the most recently received character.