Intel

®

IXP42X product line and IXC1100 control plane processors—Universal Serial Bus (USB)

v1.1 Device Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

524 Order Number: 252480-006US

18.5.23 UDC Frame Number Low Register (UFNLR)

The UDC frame number low register is the eight least-significant bits of the 11-bit

frame number contained in the last received SOF packet. The three remaining bits are

located in the UFNHR. This information is used for isochronous transfers.

These bits are updated every SOF.

18.5.24 UDC Byte Count Register 2 (UBCR2)

The Byte-Count Register maintains the remaining byte count in the active buffer of OUT

endpoint2.

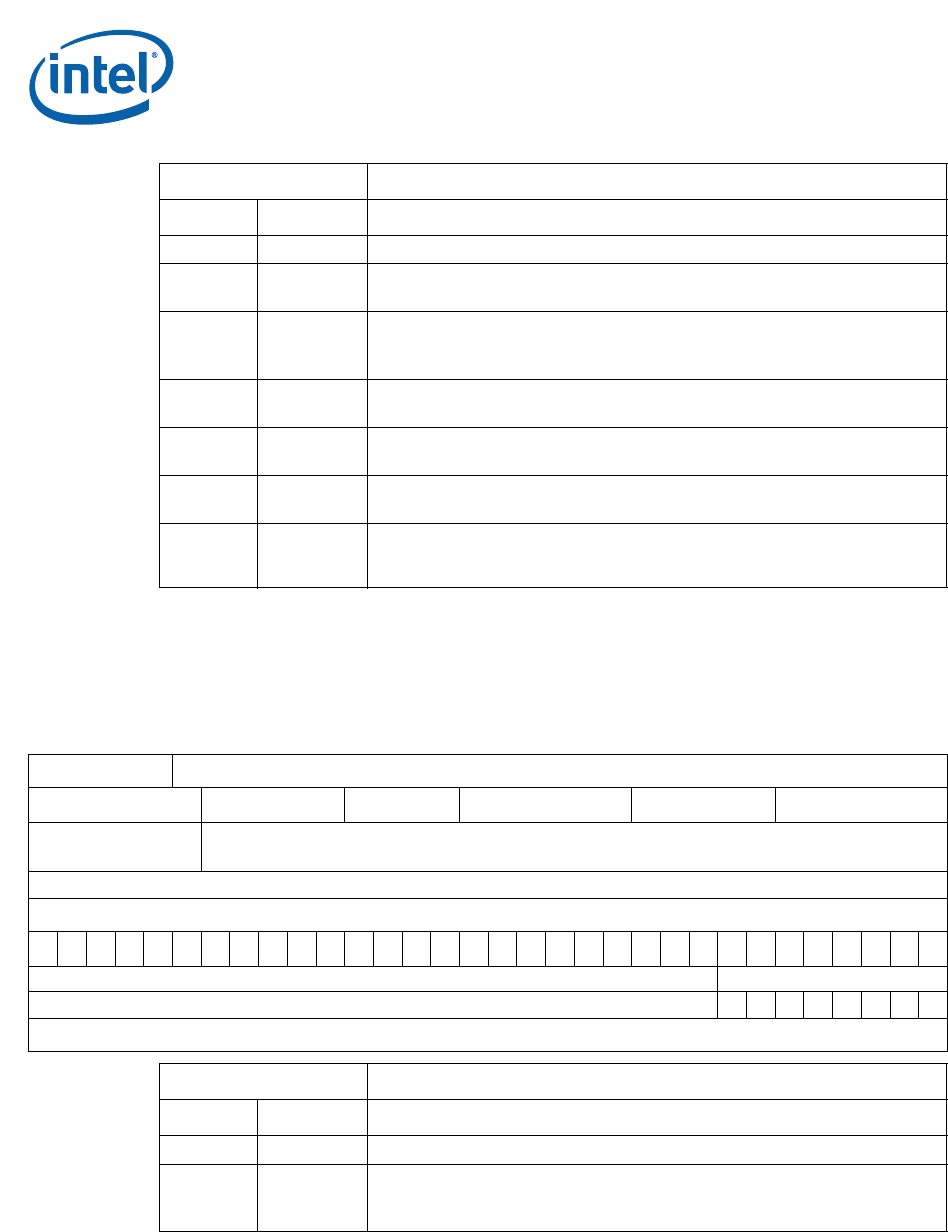

Register UFNHR

Bits Name Description

31:8 Reserved for future use.

7SIR

SOF Interrupt Request (read/write 1 to clear).

1 = SOF has been received.

6SIM

SOF interrupt mask.

0 = SOF interrupt enabled.

1 = SOF interrupt disabled.

5IPE14

Isochronous Packet Error Endpoint 14 (read/write 1 to clear).

1 = Status indicator that data in the endpoint fifo is corrupted.

4IPE9

Isochronous Packet Error Endpoint 9 (read/write 1 to clear).

1 = Status indicator that data in the endpoint fifo is corrupted.

3IPE4

Isochronous Packet Error Endpoint 4 (read/write 1 to clear).

1 = Status indicator that data in the endpoint fifo is corrupted.

2:0 FNMSB

Frame Number MSB.

Most-significant three bits of 11-bit frame number associated with last receive

SOF. Reset to all zeros.

Register Name: UFNLR

Hex Offset Address: 0 x C800B064 Reset Hex Value: 0x00000000

Register

Description:

Universal Serial Bus Device Frame Number Low Register

Access: Read-Only

Bits

31 87 0

(Reserved) 8-Bit Frame Number LSB

X 00000000

Resets (Above)

Register

UFNLR

Bits Name Description

31:8 Reserved for future use.

7.0 FNLSB

Frame number LSB.

Least significant eight bits of frame number associated with last received SOF.

Reset to all zeros.