Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

166 Order Number: 252480-006US

3.9.4.8 Semaphore Instructions

3.9.4.9 Coprocessor Instructions

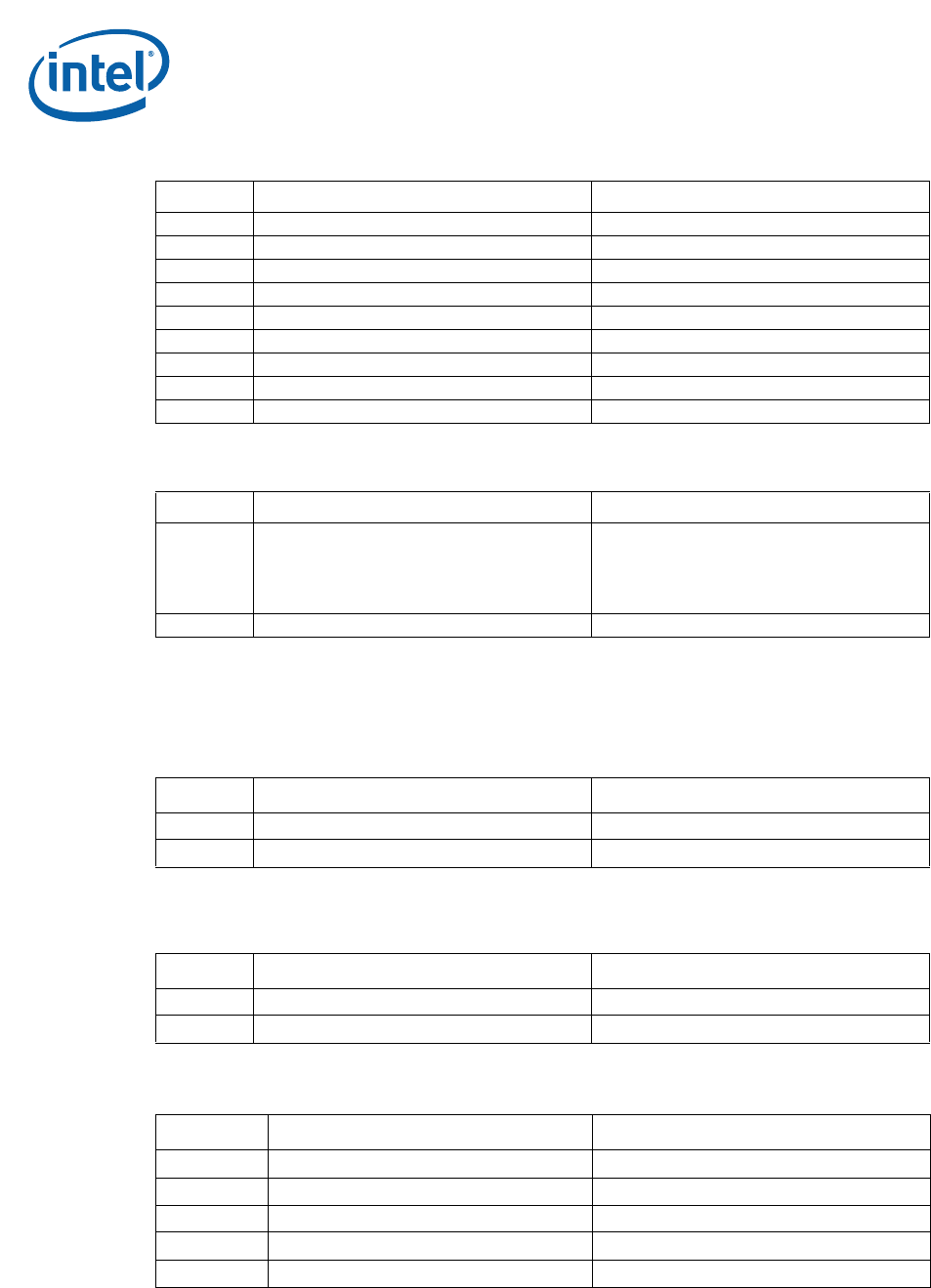

LDRSH 1 3 for load data; 1 for writeback of base

LDRT 1 3 for load data; 1 for writeback of base

PLD 1 N/A

STR 1 1 for writeback of base

STRB 1 1 for writeback of base

STRBT 1 1 for writeback of base

STRD 2 2 for write-back of base

STRH 1 1 for writeback of base

STRT 1 1 for writeback of base

Table 87. Load and Store Multiple Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency

LDM

1

2 + numreg

2

5-18 for load data (4 + numreg for last

register in list; 3 + numreg for 2nd to last

register in list; 2 + numreg for all other

registers in list);

2+ numreg for write-back of base

STM 2 + numreg 2 + numreg for write-back of base

Notes:

1. See Table 79 on page 162 for LDM timings when R15 is in the register list.

2. numreg is the number of registers in the register list.

Table 88. Semaphore Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency

SWP 5 5

SWPB 5 5

Table 89. CP15 Register Access Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency

MRC

*

44

MCR 2 N/A

Note: MRC to R15 is unpredictable.

Table 90. CP14 Register Access Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency

MRC 8 8

MRC to R15 9 9

MCR 8 N/A

LDC 11 N/A

STC 8 N/A

Table 86. Load and Store Instruction Timings

Mnemonic Minimum Issue Latency Minimum Result Latency