Intel

®

IXP42X product line and IXC1100 control plane processors—Universal Asynchronous

Receiver Transceiver (UART)

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

354 Order Number: 252480-006US

10.4.11 Modem Status Register

This register provides the current state of the control lines from the modem or data set

(or a peripheral device emulating a modem) to the processor. In addition to this current

state information, four bits of the Modem Status register provide change information.

The 3:0 bits are set to a logic 1 when a control input from the modem changes state.

The bits are reset to a logic 0 when the processor writes ones to the bits of the Modem

Status Register.

Note: When bits 0, 1, 2, or 3 are set to logic 1, a Modem Status Interrupt is generated, if bit

3 of the Interrupt Enable Register is set.

2PE

Parity Error: PE indicates that the received data character does not have the

correct even or odd parity, as selected by the even parity select bit. The PE is

set to logic 1 upon detection of a parity error and is reset to logic 0 when the

processor reads the Line Status register. In FIFO mode, PE shows a parity error

for the character at the bottom of the FIFO, not the most recently received

character.

1OE

Overrun Error: In non-FIFO mode, OE indicates that the processor did not

read data the receiver buffer register before the next character was received.

The new character is lost. In FIFO mode, OE indicates that all 64 bytes of the

FIFO are full and the most recently received byte has been discarded.

The OE indicator is set to logic 1 upon detection of an overrun condition and

reset when the processor reads the Line Status register.

0DR

Data Ready: Bit 0 is set to logic 1 when a complete incoming character has

been received and transferred into the receiver buffer register or the FIFO.

In non-FIFO mode, DR is reset to 0 when the receive buffer is read. In FIFO

mode, DR is reset to a logic 0 if the FIFO is empty (last character has been read

from RBR) or the RESETRF bit is set in the FCR.

0 = No data has been received

1 = Data is available in RBR or the FIFO

Register

LSR (Sheet 2 of 2)

Bits Name Description

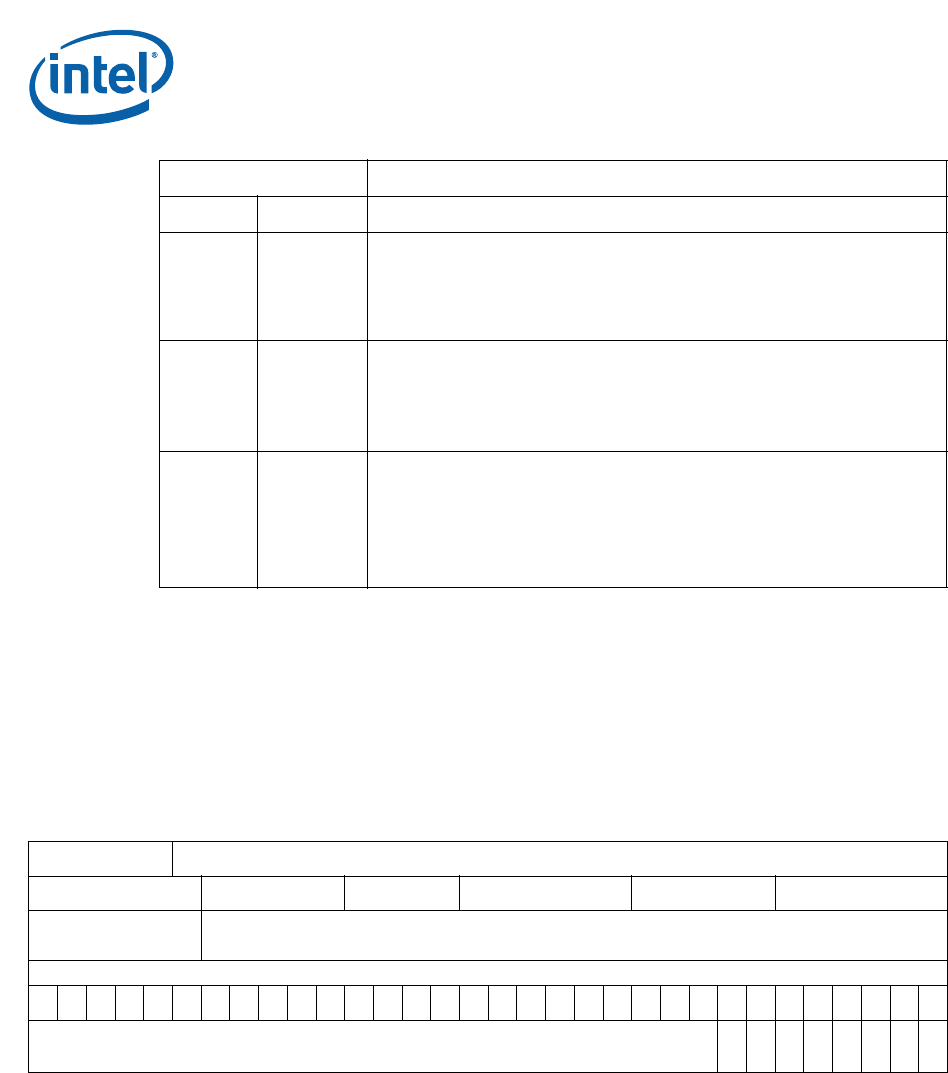

Register Name: MSR

Hex Offset Address: 0xC800 0018 Reset Hex Value: 0x00000000

Register

Description:

Modem Status Register

Access: Read Only.

31 876543210

(Reserved)

DCD

RI

DSR

CTS

DDCD

TERI

DDSR

DCTS