Intel

®

IXP42X product line and IXC1100 control plane processors—Network Processor Engines

(NPE)

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

202 Order Number: 252480-006US

4.0 Network Processor Engines (NPE)

The Network Processor Engines (NPE) are dedicated function processors containing

hardware co-processors that are integrated into the Intel

®

IXP42X Product Line of

Network Processors and IXC1100 Control Plane Processor. The NPEs are used to off

load processing functions required by the Intel XScale

®

Processor.

The Network Processor Engines are high-performance, hardware multi-threaded

processors with additional local hardware assist functionality used to off load processor

intensive functions such as MII (MAC), CRC checking/generation, AAL2, DES, 3DES,

AES, SHA-1, MD-5, etc.

Note: Certain NPEs are not available — depending on which of the IXP42X product line and

IXC1100 control plane processors is used. Table 94 shows which network-processor

models have these NPEs available.

All instruction code for the NPEs is stored locally with a dedicated instruction memory

bus and dedicated data memory bus. These engines support processing of dedicated

peripherals interfaces on the IXP42X product line and IXC1100 control plane

processors. The peripherals supported by the use of the NPEs are the 2-MII interfaces,

UTOPIA-2 interface, and two high-speed serial interfaces.

The NPE core is a hardware multi-threaded processor engine that is used to accelerate

functions that are difficult to achieve high performance in a standard RISC processor.

Each NPE core is a 133-MHz processor core that contains self-contained instruction

memory and self-contained data memory that operate in parallel.

In addition to having separate instruction/data memory and local code store, the NPE

core supports hardware multi-threading with support for multiple contexts. The support

of hardware multi-threading allows an efficient processor engine with minimal

processor stalls due to the ability of the processor core to switch context to a new

context in a single clock cycle based upon a prioritized/preemptive basis.

The prioritized/preemptive nature of the context switching allows time critical

applications to be implemented in a low-latency fashion, which is required when

processing multi-media applications. The NPE core also connects several hardware-

based co-processors. The co-processors are used to implement several functions that

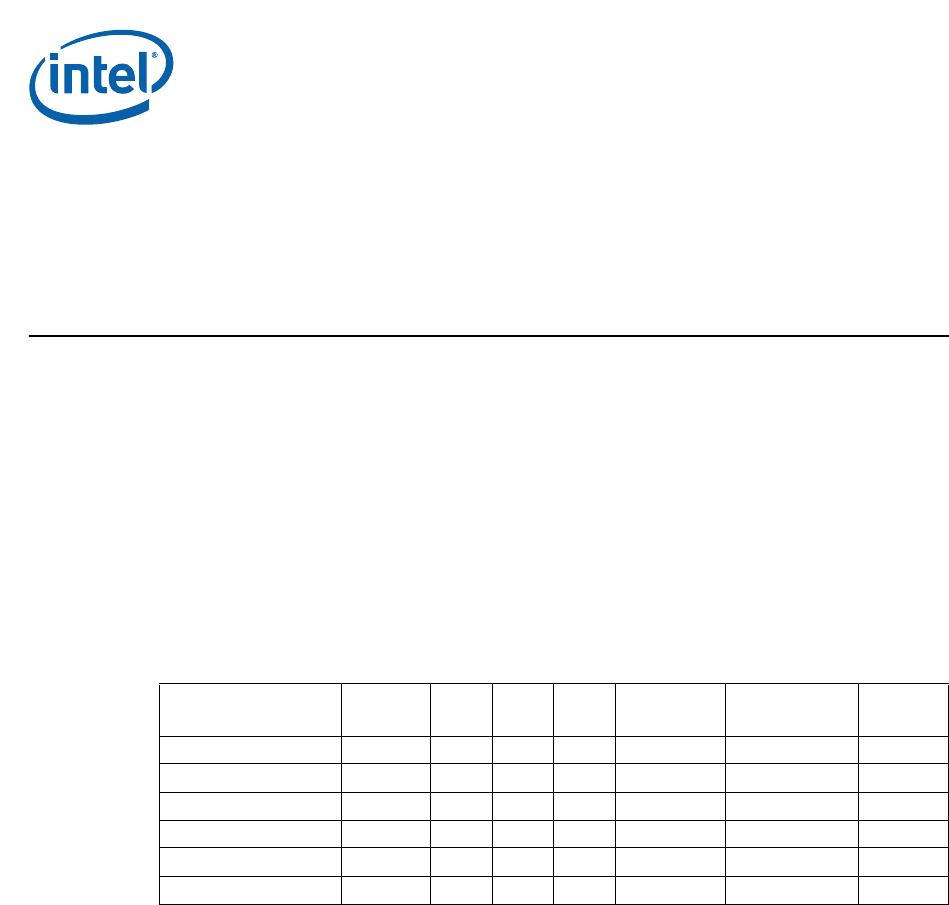

Table 94. Network Processor Functions

Device UTOPIA HSS MII 0 MII 1

AES / DES /

3DES

Multi-Channel

HDLC

SHA-1 /

MD-5

IXP425 X X X X X 8 X

IXP423 X X X X 8

IXP422 X X X X

IXP421 X X X 8

IXP420 X X

IXC1100 X X