Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

122 Order Number: 252480-006US

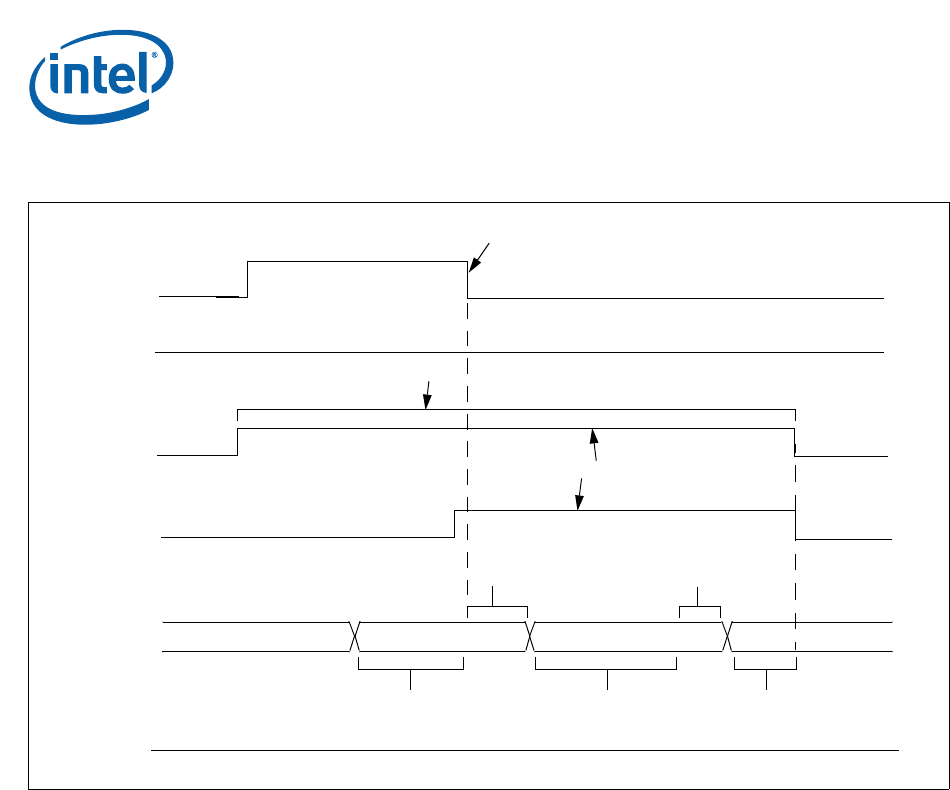

As shown in Figure 27, reset does not invalidate the instruction cache because of the

processor is in Halt Mode. Since the instruction cache was not invalidated, it may

contain valid lines. The host must avoid downloading code to virtual addresses that are

already valid in the instruction cache (mini IC or main IC), otherwise the processor may

behave unpredictably.

There are several possible solutions that ensure code is not downloaded to a VA that

already exists in the instruction cache.

Since the mini instruction cache was not invalidated, any code previously downloaded

into the mini IC is valid in the mini IC, so it is not necessary to download the same code

again.

If it is necessary to download code into the instruction cache:

1. Assert TRST.

This clears the Halt Mode bit allowing the instruction cache to be invalidated.

2. Clear the Halt Mode bit through JTAG.

This allows the instruction cache to be invalidated by reset.

3. Place the LDIC JTAG instruction in the JTAG IR, then proceed with the normal code

download, using the Invalidate IC Line function before loading each line.

This requires 10 packets to be downloaded per cache line instead of the 9 packets

described in “LDIC Cache Functions” on page 118

Figure 27. Code Download During a Warm Reset For Debug

Internal

TRST

SELDCSR JTAG IR

enter LDIC mode

RESET does not affect Mini IC (Halt Mode Bit set)

JTAG INSTR

SELDCSR LDIC

set hold_rst signal clear hold_rst signal

RESET

Reset pin

RESET pin asserted until hold_rst signal is set

hold_rst

hold_rst keeps internal reset asserted

Halt Mode

Load code into IC

clock 15 tcks after

wait 2030 tcks after

Reset deasserted

last update_dr

in LDIC mode

keep Halt Mode bit set keep Halt Mode bit set