Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 225

PCI Controller—Intel

®

IXP42X product line and IXC1100 control plane processors

6.5 PCI Controller South AHB Transactions

The PCI Controller provides access to internal functionality within the IXP42X product

line and IXC1100 control plane processors. The PCI Controller provides access to the

South AHB through the AHB Target Interface and the AHB Master Interface. The AHB

1010 X X

1011 X

1100 XX

1101 X

1110 X

1111

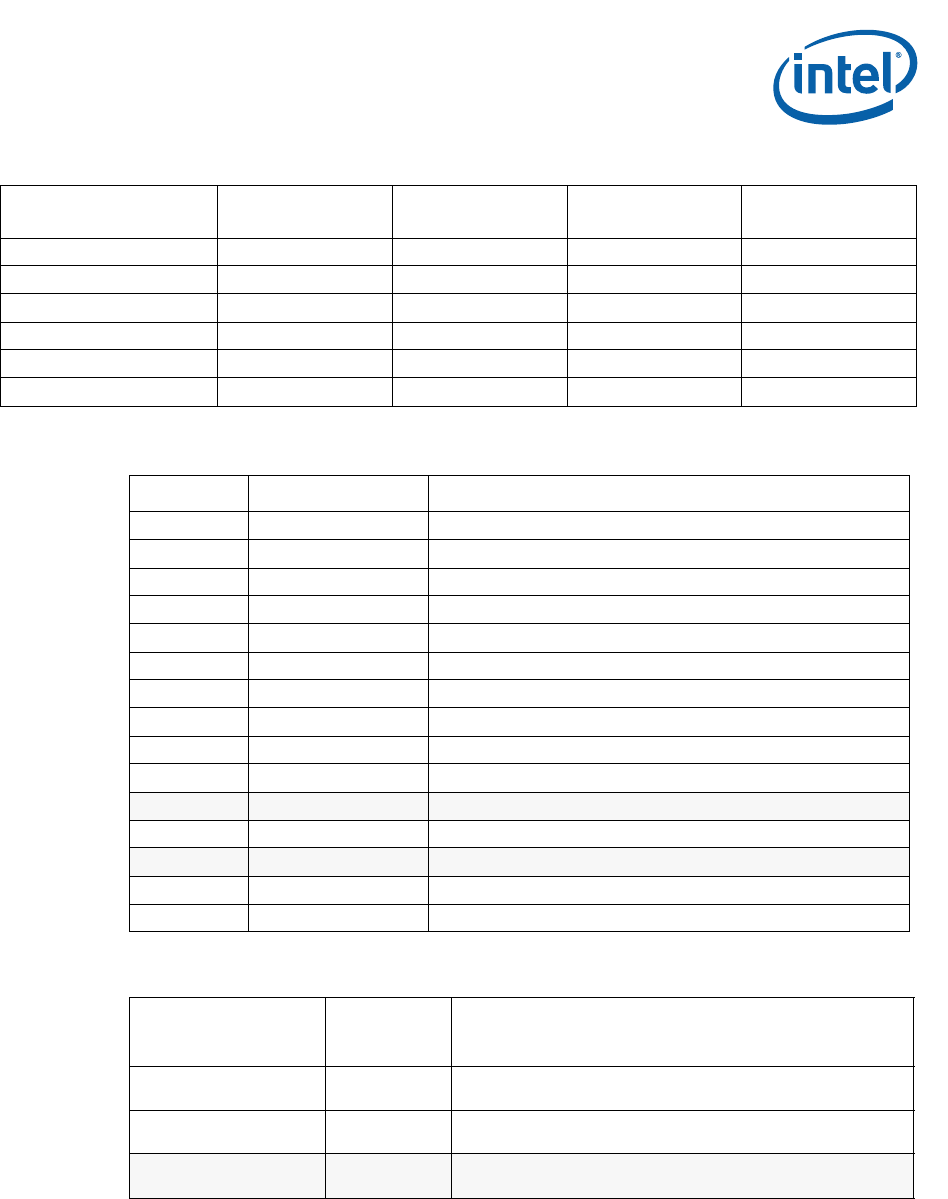

Table 101. PCI Configuration Space

Offset Register Name Description

0x00 PCI_DIDVID Device ID/Vendor ID

0x04 PCI_SRCR Status Register/Control Register

0x08 PCI_CCRID Class Code/Revision ID

0x0C PCI_BHLC BIST/Header Type/Latency Timer/Cache Line

0x10 PCI_BAR0 Base Address 0

0x14 PCI_BAR1 Base Address 1

0x18 PCI_BAR2 Base Address 2

0x1C PCI_BAR3 Base Address 3

0x20 PCI_BAR4 Base Address 4

0x24 PCI_BAR5 Base Address 5

0x28 RESERVED (Reserved)

0x2c PCI_SIDSVID Subsystem ID/Subsystem Vendor ID

0x30-38 RESERVED (Reserved)

0x3C PCI_LATINT Defines Max_Lat, Min_Gnt, Interrupt Pin, and Interrupt Line

0x40 PCI_RTOTTO Defines retry timeout and trdy timeout parameters

Table 102. Command Type for PCI Controller Configuration and Status Register Accesses

Command Value

pci_crp_ad_cbe

[19:16]

Command

Type

Description

0x0 Read

Initiates a read of the PCI Controller Configuration and Status

Register Accesses

0x1 Write

Initiates a write to the PCI Controller Configuration and Status

Register Accesses

0x2 – 0xF (Reserved)

Reserved for future use. Use of these values produce

unpredictable results.

Table 100. PCI Byte Enables Using CRP Access Method

PCI_CRP_AD_CBE(23:20

)

PCI_CRP_WDATA

(31:24)

PCI_CRP_WDATA

(24:16)

PCI_CRP_WDATA

(15:8)

PCI_CRP_WDATA

(7:0)