Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 157

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

Imprecise Data Aborts

• A data cache parity error is imprecise; the extended Status field of the Fault Status

Register is set to 0xb11000.

• All external data aborts except for those generated on a data MMU translation are

imprecise.

The Fault Address Register for all imprecise data aborts is undefined and R14_ABORT is

the address of the next instruction to execute + 4, which is the same for both ARM and

Thumb mode.

Although the Intel XScale processor guarantees the Base Restored Abort Model for

precise aborts, it cannot do so in the case of imprecise aborts. A Data Abort handler

may encounter an updated base register if it is invoked because of an imprecise abort.

Imprecise data aborts may create scenarios that are difficult for an abort handler to

recover. Both external data aborts and data cache parity errors may result in corrupted

data in the targeted registers. Because these faults are imprecise, it is possible that the

corrupted data will have been used before the Data Abort fault handler is invoked.

Because of this, software should treat imprecise data aborts as unrecoverable.

Note that even memory accesses marked as “stall until complete” (see “Details on Data

Cache and Write Buffer Behavior” on page 46) can result in imprecise data aborts. For

these types of accesses, the fault is somewhat less imprecise than the general case: it

is guaranteed to be raised within three instructions of the instruction that caused it. In

other words, if a “stall until complete” LD or ST instruction triggers an imprecise fault,

then that fault will be seen by the program within three instructions.

With this knowledge, it is possible to write code that accesses “stall until complete”

memory with impunity. Simply place several NOP instructions after such an access. If

an imprecise fault occurs, it will do so during the NOPs; the data abort handler will see

identical register and memory state as it would with a precise exception, and so should

be able to recover. An example of this is shown in Example 18 on page 158.

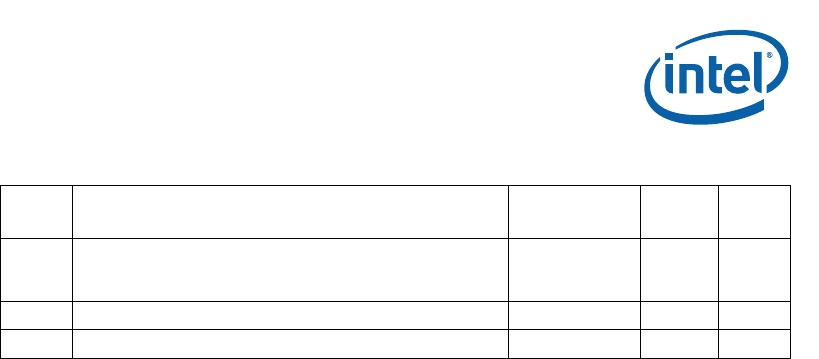

Lock Abort

This data abort occurs on an MMU lock operation (data or

instruction TLB) or on an Instruction Cache lock operation.

0b10100 invalid invalid

Imprecise External Data Abort 0b10110 invalid invalid

Lowest Data Cache Parity Error Exception 0b11000 invalid invalid

Table 75. Intel XScale

®

Processor Encoding of Fault Status for Data Aborts (Sheet 2 of 2)

Priorit

y

Sources FS[10,3:0]

*

Domain FAR

Note: All other encodings not listed in the table are reserved.