Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 351

Universal Asynchronous Receiver Transceiver (UART)—Intel

®

IXP42X product line and IXC1100

control plane processors

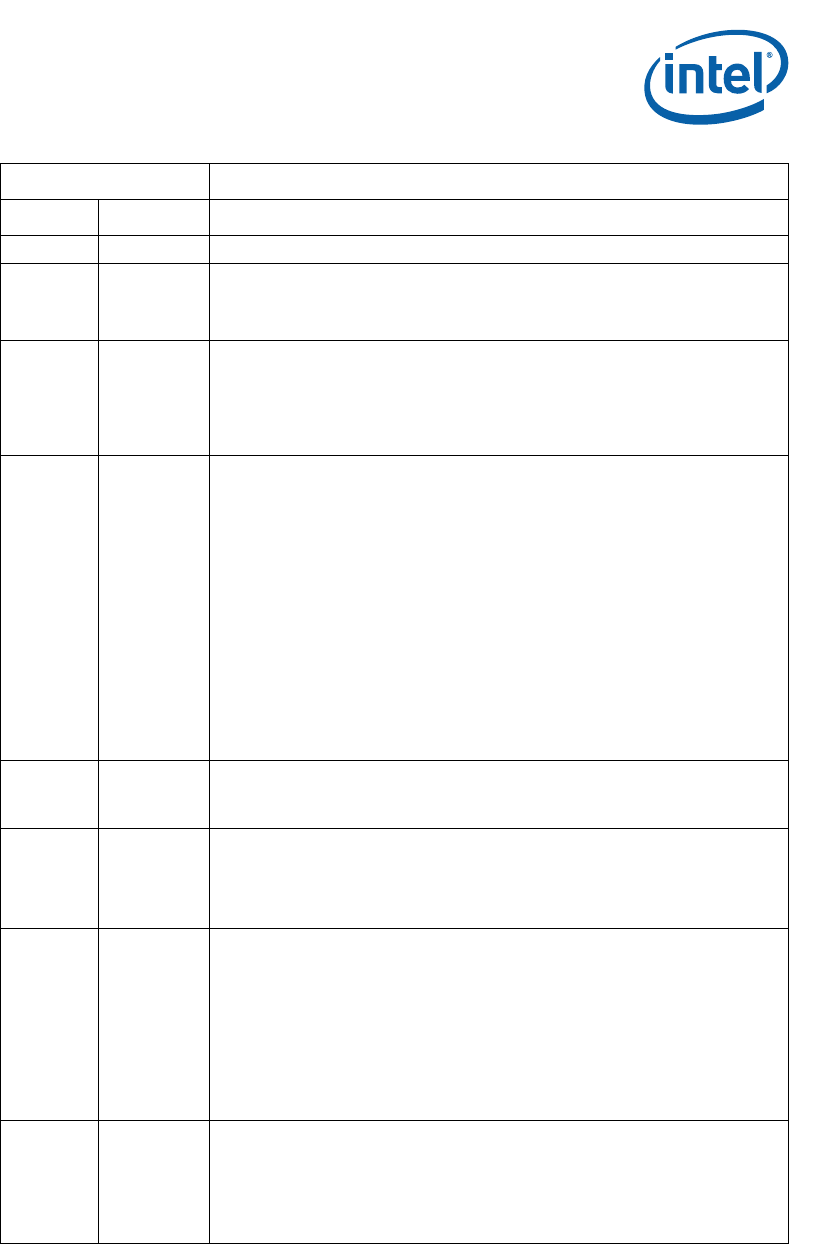

Register

LCR

Bits Name Description

31:8 (Reserved)

7DLAB

Divisor Latch Access Bit: This bit must be set to logic 1 to access the Divisor

Latches of the Baud Rate Generator during a READ or WRITE operation. It must

be set low (logic 0) to access the Receiver Buffer, the Transmit Holding Register,

or the Interrupt Enable Register.

6SB

Set break: This bit causes a break condition to be transmitted to the receiving

UART. When SB is set to logic 1, the serial output (TXD) is forced to the spacing

(logic 0) state and remains there until SB is set to logic 0. This bit acts only on

the TXD pin.

0 = No effect on TXD output

1 = Forces TXD output to 0 (space)

5STKYP

Sticky Parity: This bit is the “sticky parity” bit, which can be used in

multiprocessor communications.

When PEN and STKYP are logic 1, the bit that is transmitted in the parity bit

location (the bit just before the stop bit) is the complement of the EPS bit. If

EPS is 0, then the bit at the parity bit location will be transmitted as a 1.

In the receiver, if STKYP and PEN are logic 1, the receiver compares the bit that

is received in the parity bit location with the complement of the EPS bit. If the

values being compared are not equal, the receiver sets the Parity Error bit in

LSR and causes an error interrupt if line status interrupts were enabled. For

example, if EPS is 0, the receiver expects the bit received at the parity bit

location to be 1. If it is not, then the parity error bit is set.

By forcing the bit value at the parity bit location — rather than calculating a

parity value — a system with a master transmitter and multiple receivers can

identify some transmitted characters as receiver addresses and the rest of the

characters as data. If PEN = 0, STKYP is ignored.

0 = No effect on parity bit

1 = Forces parity bit to be opposite of EPS bit value

4EPS

Even-Parity Select:

0 = Sends or checks for odd parity

1 = Sends or checks for even parity

3PEN

Parity enable: This is the parity enable bit. When PEN is logic 1, a parity

character is generated (transmit data) or checked (receive data) between the

last data word bit and Stop bit of the serial data.

0 = No parity function

1 = Allows parity generation and checking

2STB

Stop bits: This bit specifies the number of stop bits transmitted and received in

each serial character.

If STB is a logic 0, one stop bit is generated in the transmitted data.

If STB is a logic 1 when a 5-bit word length is selected via bits 0 and 1, then 1

and one half stop bits are generated. If STB is a logic 1 when either a 6, 7, or 8-

bit word is selected, then two stop bits are generated.

The receiver checks the first stop bit only, regardless of the number of stop bits

selected.

0 = One stop bit

1 = Two stop bits, except for 5-bit character, then 1.5 bits

1:0 WLS

Word-Length Select: Specify the number of data bits in each transmitted or

received serial character.

00 = 5-bit character (default)

01 = 6-bit character

10 = 7-bit character

11 = 8-bit character