Intel

®

IXP42X product line and IXC1100 control plane processors—Internal Bus Performance

Monitoring Unit (IBPMU)

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

378 Order Number: 252480-006US

11.3 Register Descriptions

11.3.1 Event Select Register

The Event Select Register (ESR) controls the specific mode of operation of performance

monitoring. There are four general modes supported:

Each PEC counter also has three control bits. The most-significant bit indicates whether

a duration or occurrence event is to be monitored. The remaining two bits select from

four possible inputs for this configuration.

To change the monitored mode, it is necessary to write the entire ESR. The

Programmable Event Counters are reset and started when a new value is written to the

ESR and the mode is not HALT. Performance monitoring is disabled in HALT (the

default) mode. HALT mode stops all counters and the PMSR from updating. Thus

providing a stable result for reading by the processor.

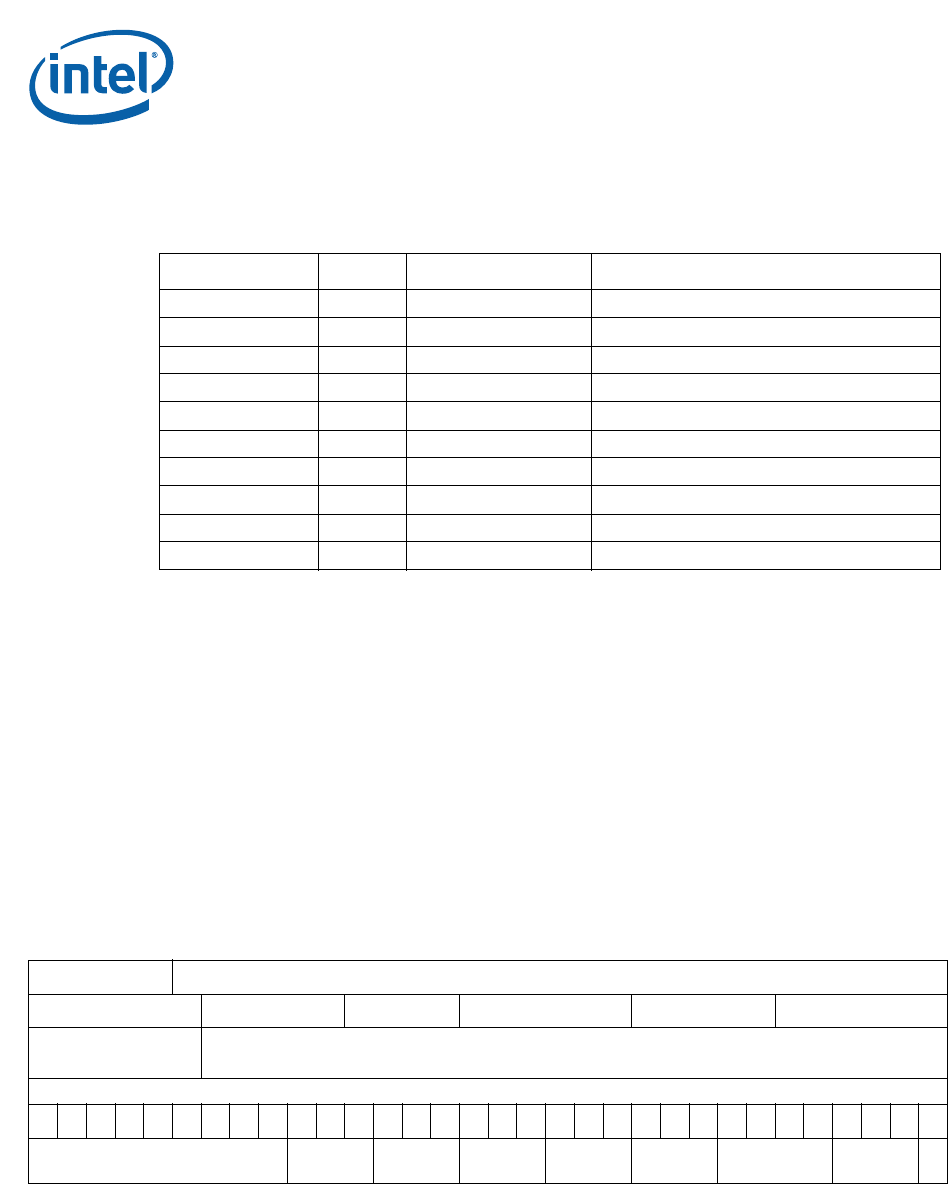

Table 143. Internal Bus PMU Register Overview

Address R/W Name Description

0xC8002000 R/W ESR Event Select Register

0xC8002004 R/COW PSR PMU Status Register

0xC8002008 R PEC1 Programmable Event Counter 1

0xC800200C R PEC2 Programmable Event Counter 2

0xC8002010 R PEC3 Programmable Event Counter 3

0xC8002014 R PEC4 Programmable Event Counter 4

0xC8002018 R PEC5 Programmable Event Counter 5

0xC800201C R PEC6 Programmable Event Counter 6

0xC8002020 R PEC7 Programmable Event Counter 7

0xC8002024 R PMSR Previous Master/Slave Register

• Halt • South

•North •SDRAM

Register Name: ESR

Hex Offset Address: 0xC800 2000 Reset Hex Value: 0x00000000

Register

Description:

Event Select Register

Access: Read/Write.

31 23 22 20 19 17 16 14 13 11 10 8 7 4 3 1 0

(Reserved) PEC1 ctrl PEC2 ctrl PEC3 ctrl PEC4 ctrl PEC5 ctrl PEC6 ctrl PEC7 ctrl

Mode