Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 483

Universal Serial Bus (USB) v1.1 Device Controller—Intel

®

IXP42X product line and IXC1100

control plane processors

18.5.2 UDC Endpoint 0 Control/Status Register (UDCCS0)

The UDC endpoint 0 control/status register contains seven bits that are used to operate

endpoint 0 (control endpoint).

18.5.2.1 OUT Packet Ready (OPR)

The OUT packet ready bit is set by the UDC when it receives a valid OUT packet to

endpoint 0. When this bit is set, the USIR0[IR0] bit will be set in the UDC status/

interrupt register if endpoint zero interrupts are enabled. This bit is cleared by writing a

1. The UDC is not allowed to enter the data phase of a transaction until this bit is

cleared.

18.5.2.2 IN Packet Ready (IPR)

The IN packet ready bit is set by the Intel XScale

®

processor if less than max_packet

bytes (16) have been written to the endpoint 0 FIFO to be transmitted. The Intel

XScale

®

processor must not set this bit if a max_packet is to be transmitted. The UDC

clears this bit when the packet has been successfully transmitted, the UDCCS0[FTF] bit

has been set, or a control OUT is received. When this bit is cleared due to a successful

IN transmission or the reception of a control OUT, the USIR0[IR0] bit in the UDC

interrupt register is set if the endpoint 0 interrupt is enabled via UICR0[IM0]. The Intel

XScale

®

processor is not able to clear UDCCS0[IPR] and always reads back a 0.

When software enables the status stage for Vendor/Class commands and control data

commands such as GET_DESCRIPTOR, GET_CONFIGURATION, GET_INTERFACE,

GET_STATUS, and SET_DECSCRIPTOR, software must also set IPR. The data in the

Transmit FIFO must be transmitted and the interrupt must be processed before the IPR

is set for the status stage.

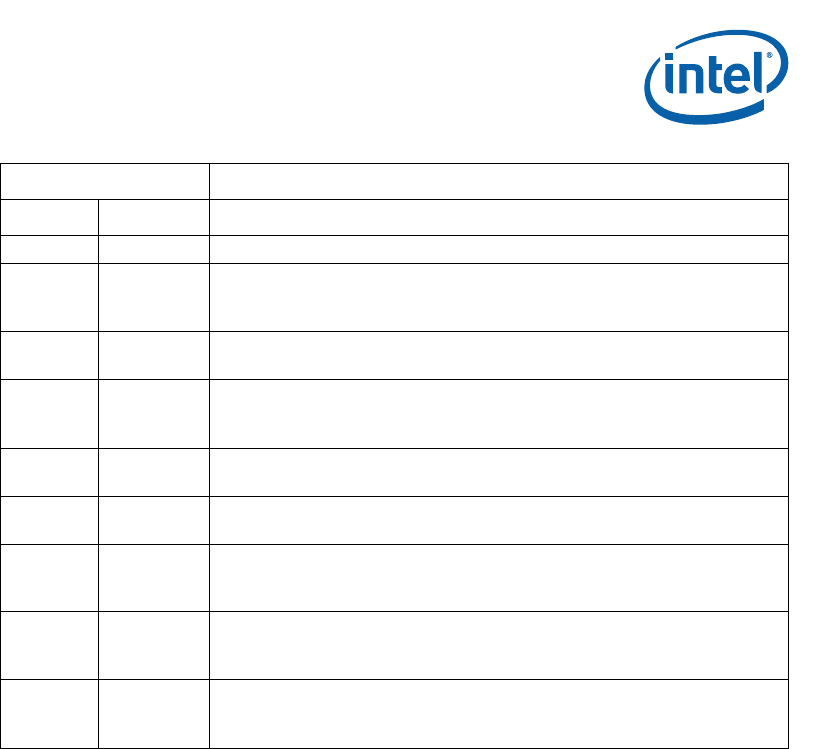

Register UDCCR

Bits Name Description

31:8 Reserved for future use

7REM

Reset interrupt mask.(read/write)

0 = Reset interrupt enabled.

1 = Reset interrupt disabled.

6RSTIR

Reset interrupt request (read/write 1 to clear).

1 = UDC was reset by the host.

5SRM

Suspend/resume interrupt mask (read/write).

0 = Suspend/resume interrupt enabled.

1 = Suspend/resume interrupt disabled.

4SUSIR

Suspend interrupt request (read/write 1 to clear).

1 = UDC received suspend signalling from the host.

3RESIR

Resume interrupt request (read/write 1 to clear).

1 = UDC received resume signalling from the host.

2RSM

Device Resume (read/write 1 to set)

0 = Maintain UDC suspend state

1= Force UDC out of suspend

1UDA

UDC active (read-only).

0 = UDC currently inactive.

1 = UDC currently active.

0UDE

UDD enable.(read/write)

0 = UDD disable

1 = UDD enabled, UDC+ and UDC- used for USB serial transmission/reception.