Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 445

Ethernet MAC A—Intel

®

IXP42X product line and IXC1100 control plane processors

§ §

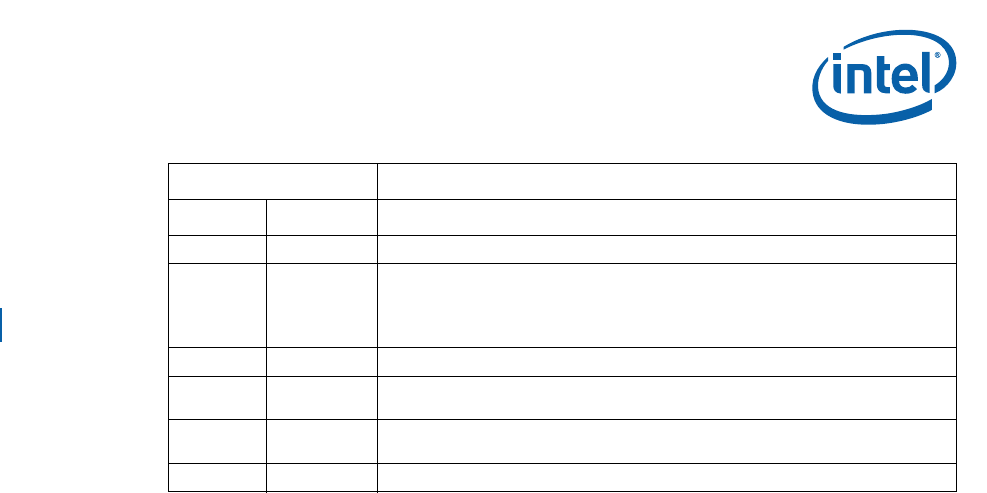

Register core_control

Bits Name Description

31:5 (Reserved)

4Mdc_en

1 = Configures the MDC as an output clock.

Set to 1 for the Intel

®

IXP42X product line and IXC1100 control plane

processors MAC A.

This bit is reserved on MAC B.

3 Send_jam 1 = Causes a jam sequence to be sent if reception of a packet begins.

2clr_tx_err

Assertion (“1”) causes the Transmit FIFO to be flushed. Data in the Transmit

FIFO is discarded.

1clr_rx_err

Assertion (“1”) causes the Receive FIFO to be flushed. Data in the Receive FIFO

is discarded.

0 rst_mac Assertion (“1”) causes the MAC to be reset.