Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 427

Ethernet MAC A—Intel

®

IXP42X product line and IXC1100 control plane processors

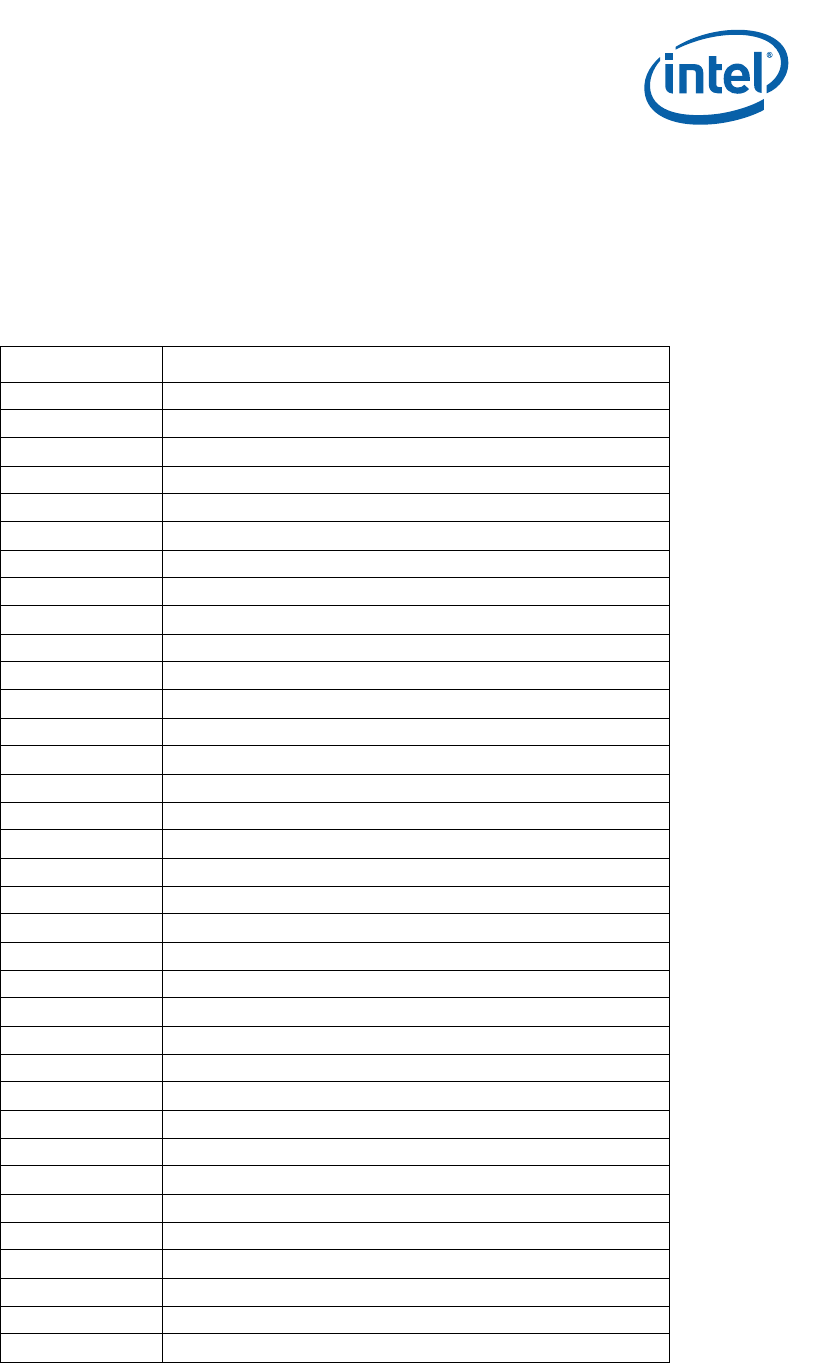

15.2 Register Descriptions

The internal registers shown below are accessible via the APB bus interface.

Unspecified addresses are reserved and should not be written; if read, a zero value will

be returned.

All of the Ethernet internal configuration and control registers are directly readable and

writeable by the Intel XScale processor via APB bus.

Address Description

0xC800 9000 Transmit Control 1

0xC800 9004 Transmit Control 2

0xC800 9010 Receive Control 1

0xC800 9014 Receive Control 2

0xC800 9020 Random Seed

0xC800 9030 Threshold For Partial Empty

0xC800 9038 Threshold For Partial Full

0xC800 9040 Buffer Size For Transmit

0xC800 9050 Transmit Single Deferral Parameters

0xC800 9054 Receive Deferral Parameters

0xC800 9060 Transmit Two Part Deferral Parameters 1

0xC800 9064 Transmit Two Part Deferral Parameters 2

0xC800 9070 Slot Time

0xC800 9080 Reserved

0xC800 9084 Reserved

0xC800 9088 Reserved

0xC800 908C Reserved

0xC800 9090 Reserved

0xC800 9094 Reserved

0xC800 9098 Reserved

0xC800 909C Reserved

0xC800 90A0 Address Mask 1

0xC800 90A4 Address Mask 2

0xC800 90A8 Address Mask 3

0xC800 90AC Address Mask 4

0xC800 90B0 Address Mask 5

0xC800 90B4 Address Mask 6

0xC800 90C0 Address 1

0xC800 90C4 Address 2

0xC800 90C8 Address 3

0xC800 90CC Address 4

0xC800 90D0 Address 5

0xC800 90D4 Address 6

0xC800 90E0 Threshold For Internal Clock

0xC800 90F0 Unicast Address 1