Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 169

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

3.10.2.1.2 Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane

Processor Pipeline Organization

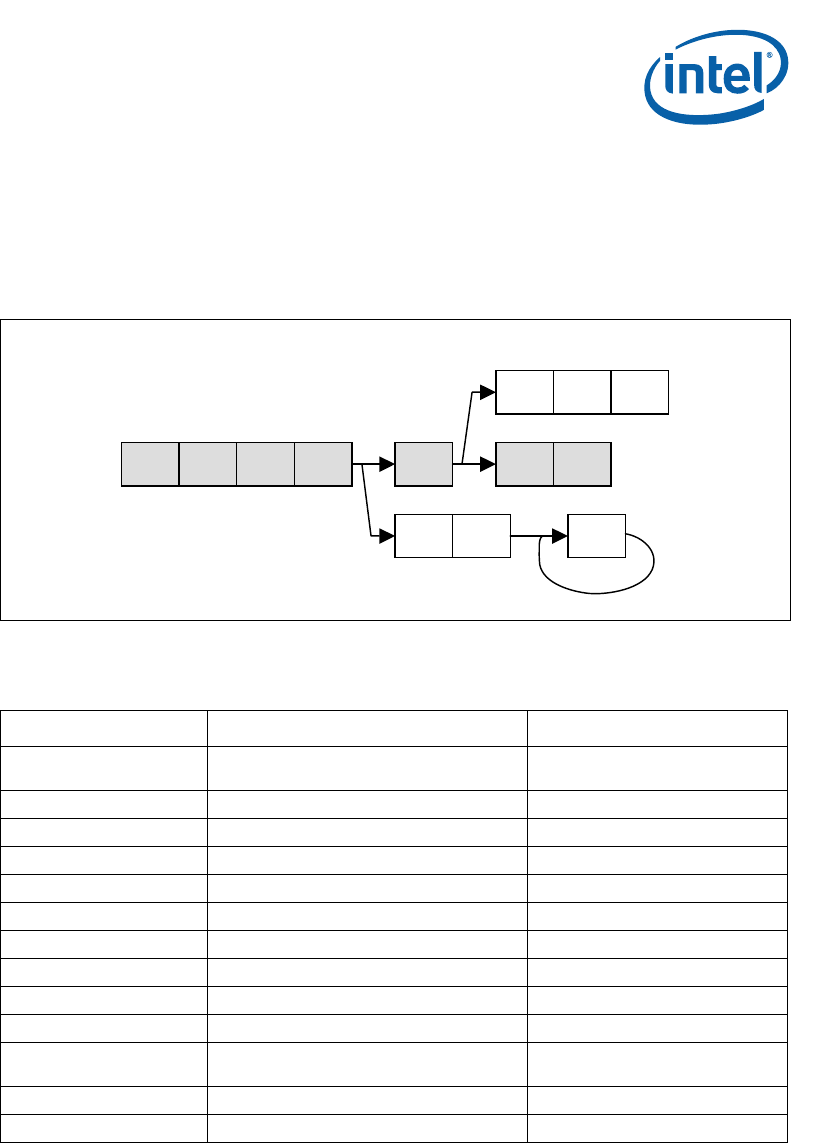

The IXP42X product line and IXC1100 control plane processors single-issue super-

pipeline consist of a main execution pipeline, MAC pipeline, and a memory access

pipeline. These are shown in Figure 29, with the main execution pipeline shaded.

Table 93 gives a brief description of each pipe-stage.

3.10.2.1.3 Out-of-Order Completion

Sequential consistency of instruction execution relates to two aspects: first, to the

order in which the instructions are completed; and second, to the order in which

memory is accessed due to load and store instructions. The IXP42X product line and

IXC1100 control plane processors preserve a weak processor consistency because

instructions may complete out of order, provided that no data dependencies exist.

Figure 29. Processors’ RISC Super-Pipeline

F1 F2 ID RF X1 X2

XWB

M1 M2 Mx

D1 D2

DWB

Main execution pipeline

MAC pipeline

Memory pipeline

Table 93. Pipelines and Pipe Stages

Pipe / Pipe State Description Covered In

Main Execution Pipeline Handles data processing instructions

“Main Execution Pipeline” on

page 171

IF1/IF2 Instruction Fetch “

ID Instruction Decode “

RF Register File / Operand Shifter “

X1 ALU Execute “

X2 State Execute “

XWB Write-back “

Memory Pipeline Handles load/store instructions “Memory Pipeline” on page 172

D1/D2 Data Cache Access “

DWB Data cache writeback “

MAC Pipeline Handles all multiply instructions

“Multiply/Multiply Accumulate

(MAC) Pipeline” on page 173

M1-M5 Multiplier stages “

MWB (not shown) MAC write-back - may occur during M2-M5 “