Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 81

Intel XScale

®

Processor—Intel

®

IXP42X product line and IXC1100 control plane processors

3.5.1.7 Register 6: Fault Address Register

3.5.1.8 Register 7: Cache Functions

All the functions defined in existing ARM products appear here. The Intel XScale

processor adds other functions as well. This register should be accessed as write-only.

Reads from this register, as with an MRC, have an undefined effect.

The Drain Write Buffer function not only drains the write buffer but also drains the fill

buffer.

The Intel XScale processor does not check permissions on addresses supplied for cache

or TLB functions. Due to the fact only privileged software may execute these functions,

full accessibility is assumed. Cache functions will not generate any of the following:

• Translation faults

• Domain faults

• Permission faults

The invalidate instruction cache line command does not invalidate the BTB. If software

invalidates a line from the instruction cache and modifies the same location in external

memory, it needs to invalidate the BTB also. Not invalidating the BTB in this case may

cause unpredictable results.

Disabling/enabling a cache has no effect on contents of the cache: valid data stays

valid, locked items remain locked. All operations defined in Table 18 work regardless of

whether the cache is enabled or disabled.

Since the Clean DCache Line function reads from the data cache, it is capable of

generating a parity fault. The other operations will not generate parity faults.

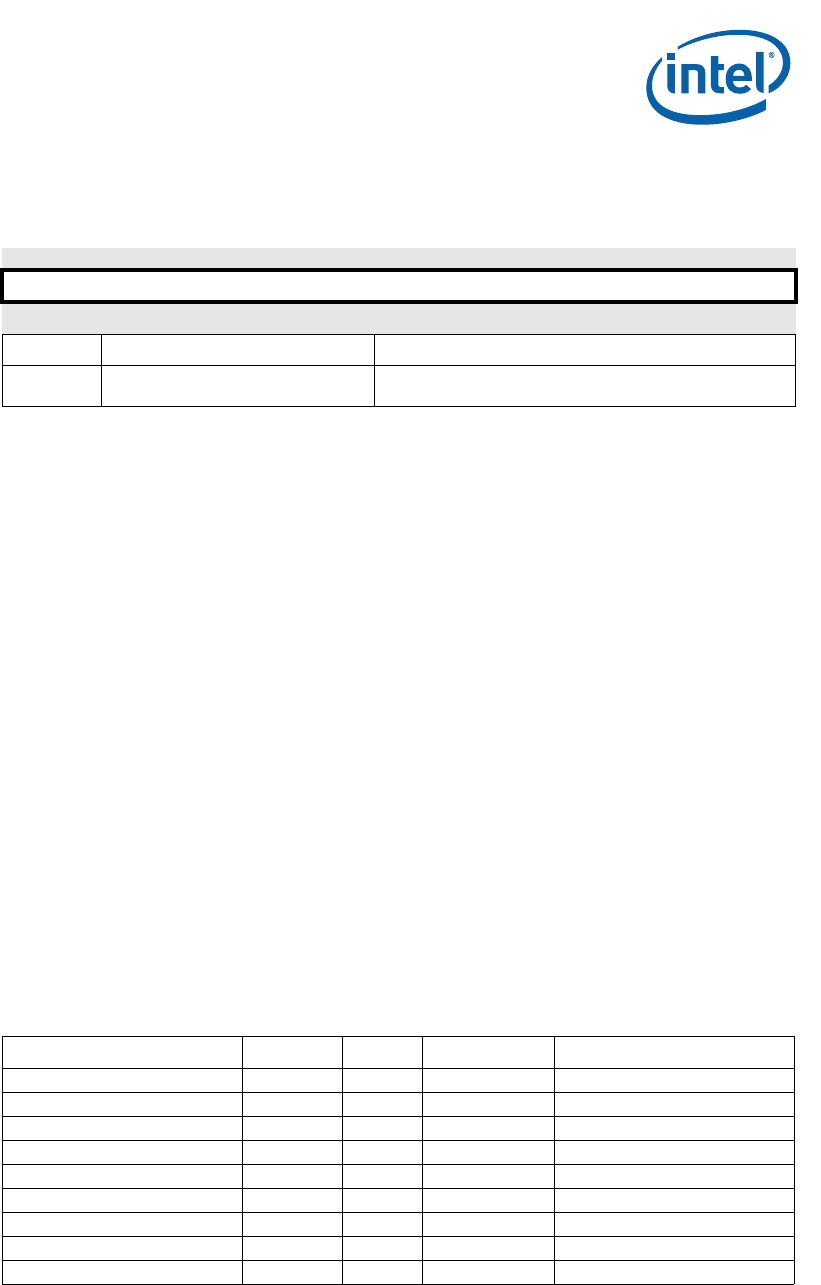

Table 17. Fault Address Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Fault Virtual Address

reset value: unpredictable

Bits Access Description

31:0 Read / Write

Fault Virtual Address - Contains the MVA of the data

access that caused the memory abort

Table 18. Cache Functions

Function opcode_2 CRm Data Instruction

Invalidate I&D cache & BTB 0b000 0b0111 Ignored MCR p15, 0, Rd, c7, c7, 0

Invalidate I cache & BTB 0b000 0b0101 Ignored MCR p15, 0, Rd, c7, c5, 0

Invalidate I cache line 0b001 0b0101 MVA MCR p15, 0, Rd, c7, c5, 1

Invalidate D cache 0b000 0b0110 Ignored MCR p15, 0, Rd, c7, c6, 0

Invalidate D cache line 0b001 0b0110 MVA MCR p15, 0, Rd, c7, c6, 1

Clean D cache line 0b001 0b1010 MVA MCR p15, 0, Rd, c7, c10, 1

Drain Write (& Fill) Buffer 0b100 0b1010 Ignored MCR p15, 0, Rd, c7, c10, 4

Invalidate Branch Target Buffer 0b110 0b0101 Ignored MCR p15, 0, Rd, c7, c5, 6

Allocate Line in the Data Cache 0b101 0b0010 MVA MCR p15, 0, Rd, c7, c2, 5