Intel

®

IXP42X product line and IXC1100 control plane processors—Overview of Product Line

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

36 Order Number: 252480-006US

The IXP42X product line and IXC1100 control plane processors have been equipped to

efficiently handle audio processing through the support of 16-bit data types and 16-bit

operations. These audio-coding enhancements center around multiply and accumulate

operations which accelerate many of the audio filter operations.

2.1.1 Intel XScale

®

Processor Overview

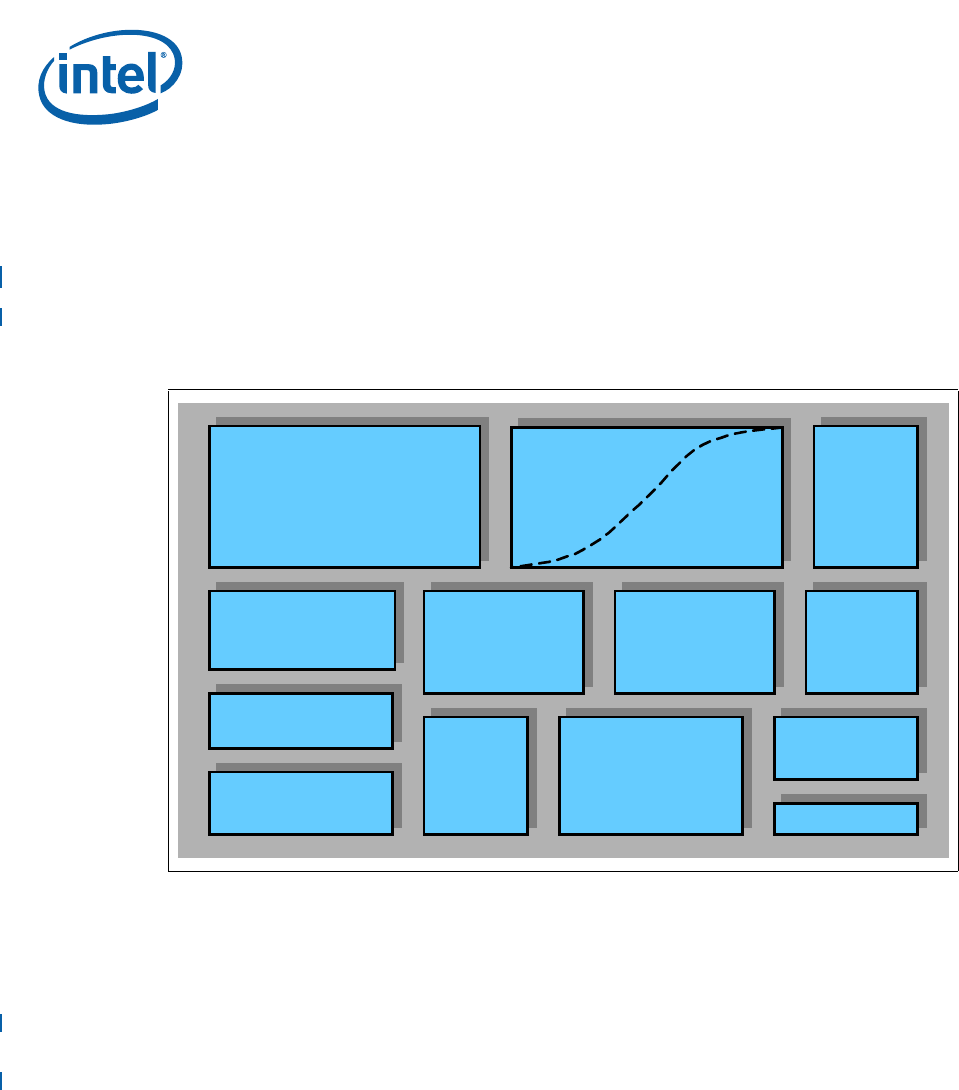

Figure 6 shows the major functional blocks of the Intel XScale processor. This section

gives brief, high-level overviews of these blocks.

Note: The Power Management Control feature was not implemented in the IXP42X product

line and IXC1100 control plane processors.

2.1.1.1 ARM

*

Compatibility

ARM

*

Version 5 Architecture added floating point instructions to ARM Version 4. The

Intel XScale processor implements the integer instruction set architecture of ARM V5,

but does not provide hardware support of the floating point instructions.

Intel XScale processor provides the Thumb* instruction set (ARM V5T) and the ARM

V5E DSP extensions.

Backward compatibility with ARM products is maintained for user-mode applications.

Operating systems may require modifications to match the specific hardware features

of the IXP42X product line and IXC1100 control plane processors and to take

advantage of added performance enhancements.

2.1.1.2 Multiply/Accumulate (MAC)

The MAC unit supports early termination of multiplies/accumulates in two cycles and

can sustain a throughput of a MAC operation every cycle. Several architectural

enhancements were made to the MAC to support audio coding algorithms, which

include a 40-bit accumulator and support for 16-bit packed data.

Figure 6. Intel XScale

®

Technology Architecture Features

Write Buffer

• 8 entries

• Full coalescing

Fill

Buffer

• 4 - 8 entries

Instruction Cache

• 32K or 16K bytes

• 32 ways

• Lockable by line

IMMU

• 32 entry TLB

• Fully associative

• Lockable by entry

DMMU

• 32 entry TLB

• Fully Associative

• Lockable by entry

JTAG

Debug

• Hardware Breakpoints

• Branch History Table

Branch Target

Buffer

• 128 entries

MAC

• Single Cycle

Throughput (16*32)

• 16-bit SIMD

• 40 bit Accumulator

Data Cache

• 32K or 16K bytes

• 32 ways

• wr-back or

wr-through

• Hit under

miss

Data RAM

• 28K or 12K

bytes

• Re-map of data

cache

Power

Mgnt

Ctrl

Mini-

Data

Cache

• 2K or 1K

bytes

• 2 ways

Performance

Monitoring