Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

90 Order Number: 252480-006US

3.6.3.1 Halt Mode

When the debug unit is configured for halt mode, the reset vector is overloaded to

serve as the debug vector. A new processor mode, DEBUG mode (CPSR[4:0] = 0x15),

is added to allow debug exceptions to be handled similarly to other types of ARM

exceptions.

When a debug exception occurs, the processor switches to debug mode and redirects

execution to a debug handler, via the reset vector. After the debug handler begins

execution, the debugger can communicate with the debug handler to examine or alter

processor state or memory through the JTAG interface.

The debug handler can be downloaded and locked directly into the instruction cache

through JTAG so external memory is not required to contain debug handler code.

3.6.3.2 Monitor Mode

In monitor mode, debug exceptions are handled like ARM prefetch aborts or ARM data

aborts, depending on the cause of the exception.

When a debug exception occurs, the processor switches to abort mode and branches to

a debug handler using the pre-fetch abort vector or data abort vector. The debugger

then communicates with the debug handler to access processor state or memory

contents.

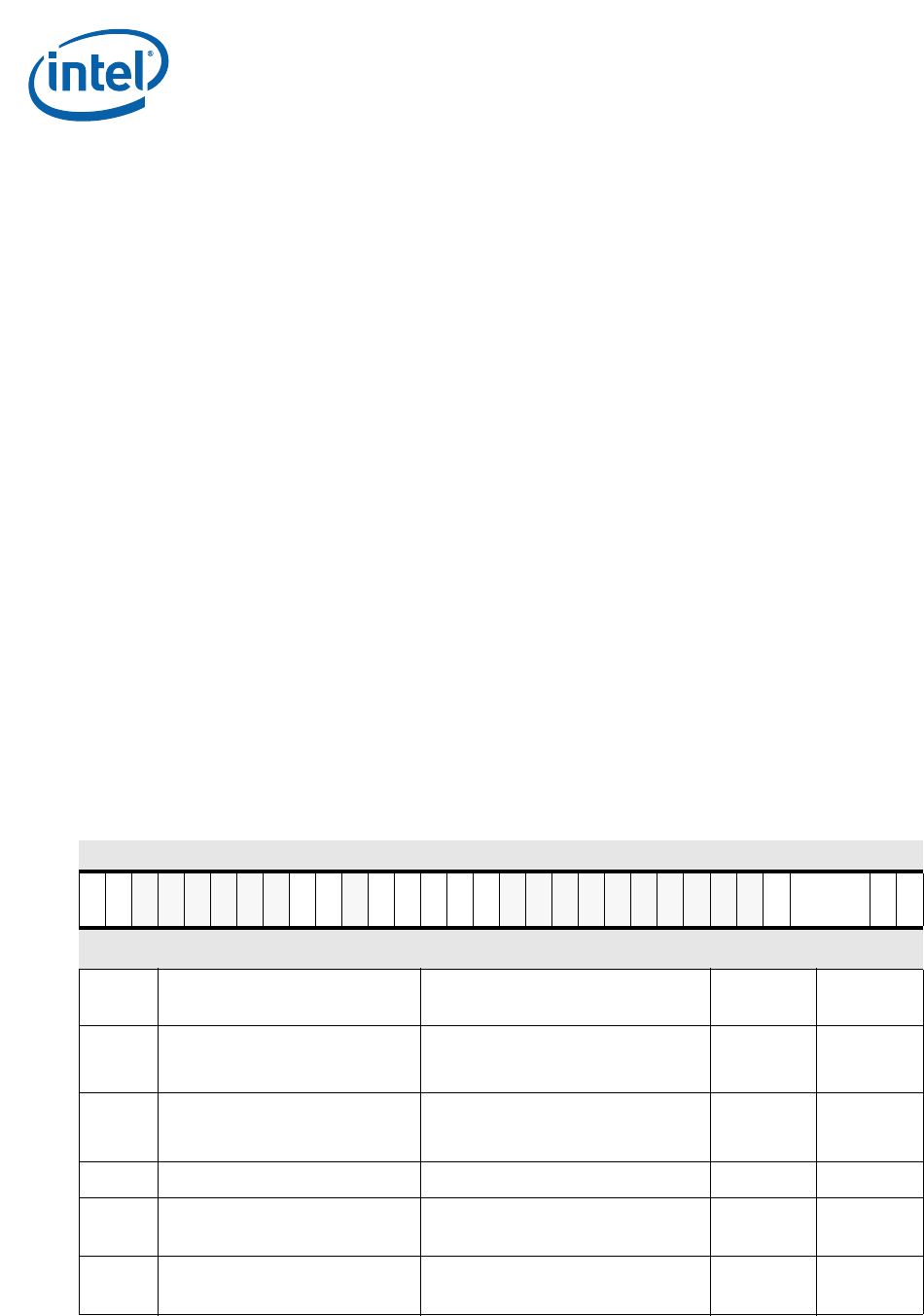

3.6.4 Debug Control and Status Register (DCSR)

The DCSR register is the main control register for the debug unit. Table 33 shows the

format of the register. The DCSR register can be accessed in privileged modes by

software running on the processor or by a debugger through the JTAG interface. Refer

to “SELDCSR JTAG Register” on page 103 for details about accessing DCSR through

JTAG.

Table 33. Debug Control and Status Register (DCSR) (Sheet 1 of 2)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

G

E

H

T

F

T

I

T

D

T

A

T

S

T

U

T

R

S

A

MOE M E

Bits Access Description

Reset

Value

TRST

Value

31

SW Read / Write

JTAG Read-Only

Global Enable (GE)

0: disables all debug functionality

1: enables all debug functionality

0

unchange

d

30

SW Read Only

JTAG Read / Write

Halt Mode (H)

0: Monitor Mode

1: Halt Mode

unchange

d

0

29:24 Read-undefined / Write-As-Zero Reserved

undefined undefined

23

SW Read Only

JTAG Read / Write

Trap FIQ (TF)

unchange

d

0

22

SW Read Only

JTAG Read / Write

Trap IRQ (TI)

unchange

d

0