Intel

®

IXP42X product line and IXC1100 control plane processors—UTOPIA Level-2

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

542 Order Number: 252480-006US

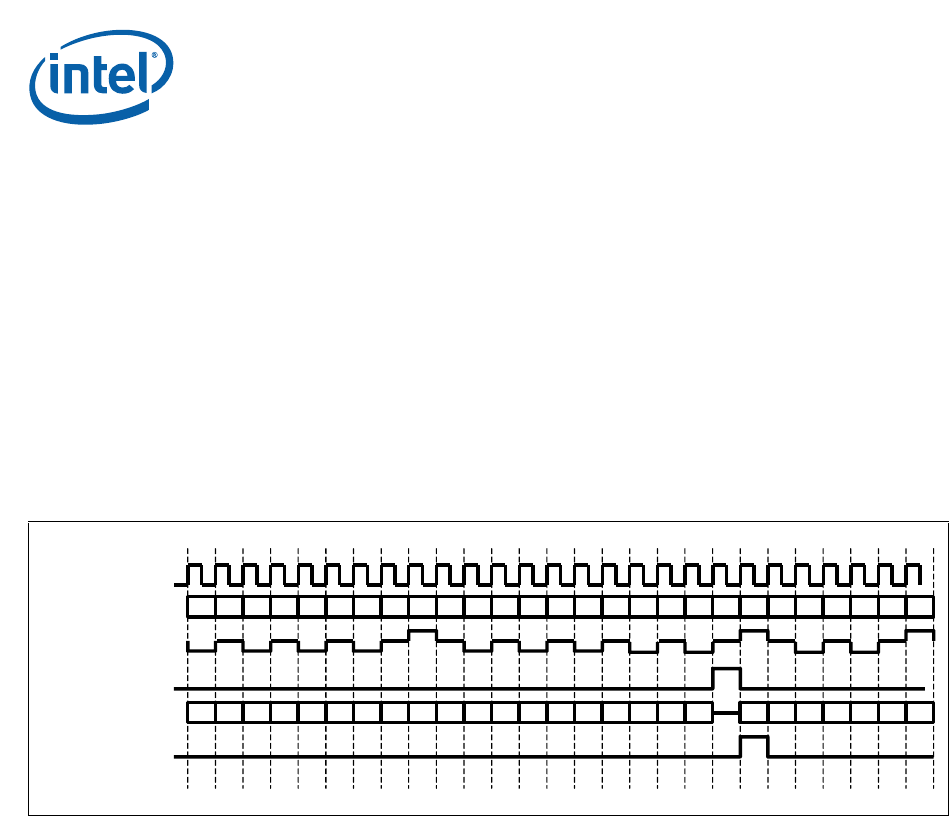

• There are eight active physical interfaces connected, named A through H, that map

to logical address 0 through 7.

• Physical Interface A is the currently selected physical interface for clock cycles 0

through18.

• Notice on clock 8 that the result from Physical Interface G is that Physical Interface

G is ready to receive a cell. The UTP_TX_FCI signal flags that a full cell can be sent

to Physical Interface G by the Physical Interface asserting the UTP_TX_FCI to logic

1 one clock after Physical Interface G has been polled.

• On clock 17, the final Physical Interface polled is the Physical Interface that is

currently selected. This polling is irrelevant to the Physical Interface that was polled

previously prior to this location.

• Notice on clock cycles 19 and 20 that Physical Interface G is selected as the next

Physical Interface that the IXP42X product line and IXC1100 control plane

processors will transmit data to.

In cell-level single-PHY (SPHY) mode the physical interface indicates that it can accept

a cell by asserting the UTP_OP_FCI (also known as TX_FULL_N/TX_CLAV) signal. The

UTOPIA Level-2 Interface subsequently transmits a cell to the PHY at the same time

asserting UTP_OP_FCO (a.k.a.TX_ENB_N).

For more timing diagrams and more details on operation in single-PHY (SPHY) mode of

operation, see the UTOPIA Level-2, Revision 1.0 Specification.

When using the UTOPIA Level-2 Interface in single-PHY (SPHY) mode the

UTP_TX_ADDR is driven with an address of all logic 1s and the UTP_RX_ADDR must be

driven with all logic 1s.

In octet-level single-PHY (SPHY) mode, the physical interface indicates to the UTOPIA

Level-2 Interface on the IXP42X product line and IXC1100 control plane processors

that the physical interface can accept data by de-asserting UTP_OP_FCI (also known as

TX_FULL_N/TX_CLAV) signal. The UTOPIA Level-2 Interface subsequently transmits

data to the PHY at the same time, asserting UTP_OP_FCO (also known as TX_ENB_N).

When the physical interface de-asserts UTP_OP_FCI (also known as TX_FULL_N/

TX_CLAV), it indicates to the UTOPIA Level-2 Interface that the physical interface will

only accept four more bytes of data.

For more timing diagrams and details on the single-PHY (SPHY) mode of operation, see

the UTOPIA Level-2, Revision 1.0 Specification.

Figure 98. UTOPIA Level-2 MPHY Transmit Polling

UTP_TX_CLK

UTP_TX_ADDR (4:0)

UTP_TX_FCI

(a.k.a. – TX_CLAV)

UTP_TX_FCO

(a.k.a. – TX_ENB_N)

UTP_TX_DATA(7:0)

UTP_TX_SOC

535251494847464544434241 40 39 38 3736 35 65

4

3 2 1 7

50

A

X

C

X

B

X

A

X

H

X

G

X

F

X

E

X

D

X

X

E

X

D

X

G

X

F

X

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 24 25 26 27