Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

138 Order Number: 252480-006US

3.7.3 Managing the Performance Monitor

The following are a few notes about controlling the performance monitoring

mechanism:

• An interrupt request will be generated when a counter’s overflow flag is set and its

associated interrupt enable bit is set in INTEN. The interrupt request will remain

asserted until software clears the overflow flag by writing a one to the flag that is

set. (Note that the product specific interrupt unit and the CPSR must have enabled

the interrupt in order for software to receive it.) The interrupt request can also be

deasserted by clearing the corresponding interrupt enable bit. Disabling the facility

(PMNC.E) doesn’t deassert the interrupt request.

• The counters continue to record events even after they overflow.

• To change an event for a performance counter, first disable the facility (PMNC.E)

and then modify EVTSEL. Not doing so will cause unpredictable results.

• To increase the monitoring duration, software can extend the count duration

beyond 32 bits by counting the number of overflow interrupts each 32-bit counter

generates. This can be done in the interrupt service routine (ISR) where an

increment to some memory location every time the interrupt occurs will enable

longer durations of performance monitoring. This does intrude upon program

execution but is negligible, since the ISR execution time is in the order of tens of

cycles compared to the number of cycles it took to generate an overflow interrupt

(2

32

).

• Power can be saved by selecting event 0xFF for any unused event counter. This

only applies when other event counters are in use. When the performance monitor

is not used at all (PMNC.E = 0x0), hardware ensures minimal power consumption.

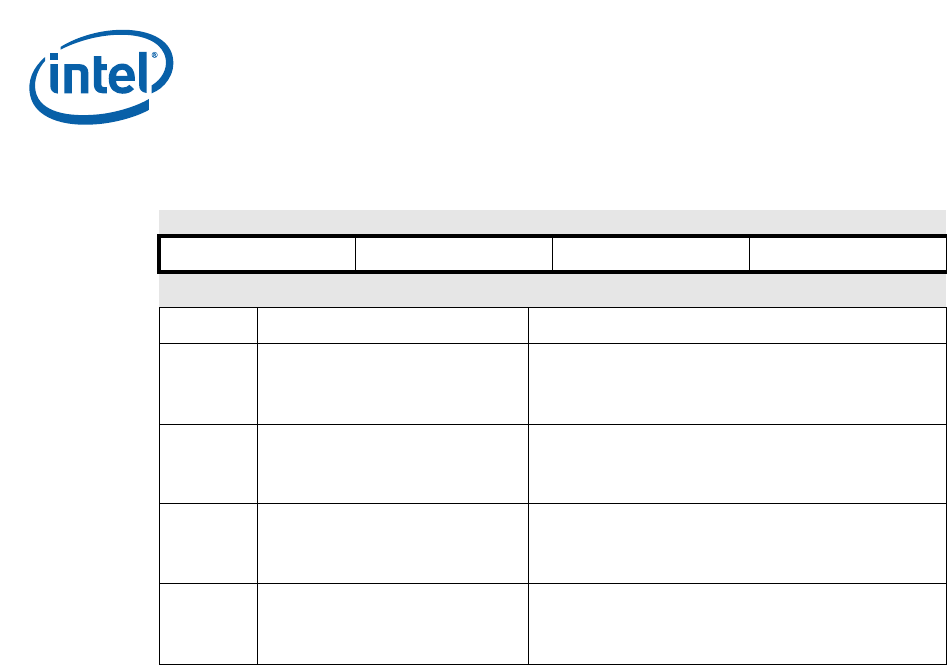

Table 59. Event Select Register

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

evtCount3 evtCount2 evtCount1 evtCount0

reset value: unpredictable

Bits Access Description

31:24 Read / Write

Event Count 3 (evtCount3) -

Identifies the source of events that PMN3 counts. See

Table 60 for a description of the values this field may

contain.

23:16 Read / Write

Event Count 2 (evtCount2) -

Identifies the source of events that PMN2 counts. See

Table 60 for a description of the values this field may

contain.

15:8 Read / Write

Event Count 1 (evtCount1) -

Identifies the source of events that PMN1 counts. See

Table 60 for a description of the values this field may

contain.

7:0 Read / Write

Event Count 0 (evtCount0) -

Identifies the source of events that PMN0 counts. See

Table 60 for a description of the values this field may

contain.