Intel

®

IXP42X product line and IXC1100 control plane processors—Internal Bus Performance

Monitoring Unit (IBPMU)

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

374 Order Number: 252480-006US

The programmable event counters (PEC) and the previous master and slave register

(PMSR) can be used for easy collection of the gathered statistical information.

The programmable event counters can be read periodically or when an interrupt occurs

to the Intel

®

IXP42X product line and IXC1100 control plane processors’ Interrupt

Controller. An interrupt will occur when any of the programmable event counters roll

over their maximum count value.

Writing logic 1 to the PMU status register bit — associated with the overflow condition

that caused the interrupt to occur — clears the interrupt. The information obtained by

reading the programmable event counters is entirely dependent on how the IBPMU is

initialized in the event select register.

The IBPMU can be configured to monitor occurrence events. An occurrence event

causes the programmable event counter to increase by one, each time the event

occurs. Table 140 lists the various occurrence events that can be monitored by the

IXP42X product line and IXC1100 control plane processors.

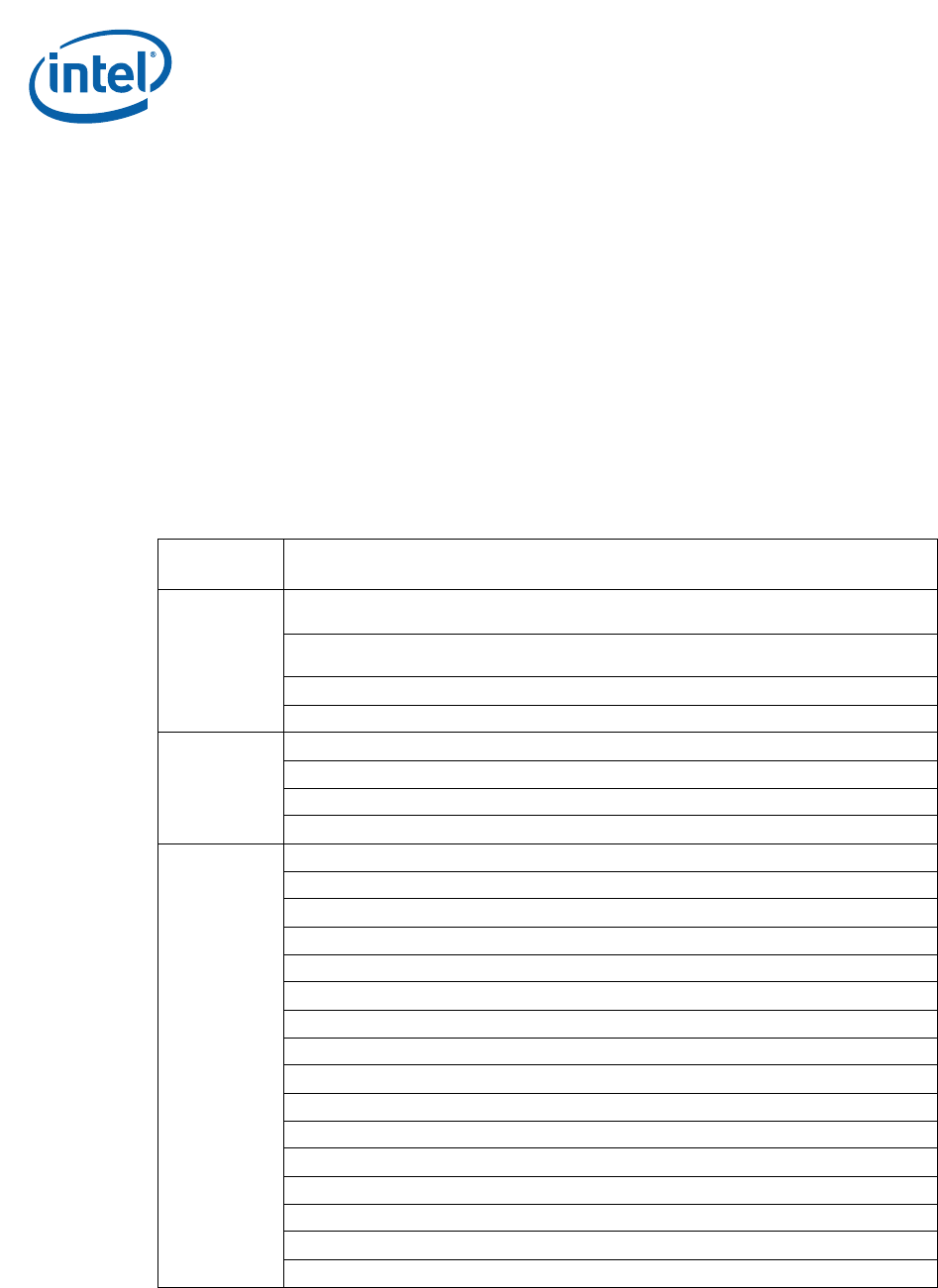

Table 140. Occurrence Events

Observed

Interface

Monitored Event

AHB_South

Number of grants to the Intel XScale processor, AHB_Bridge, APB bridge and

PCI_Controller.

Number of transactions initiated by the Intel XScale processor, AHB_Bridge, APB bridge and

PCI_Controller

Number of retries Signaled by the PCI_Controller and Expansion_bus to the initiators.

Number of split transfers claimed by the PCI_Controller and Expansion_Bus to the initiators

AHB_North

Number of grants to NPE A, NPE B and NPE C

Number of transactions initiated by NPE A, NPE B and NPE C.

Number of retries signaled by the AHB_Bridge to the initiators.

Number of split transfers claimed by the AHB_Bridge to the initiators

SDRAM

Number of SDR0 misses

Number of SDR1 misses

Number of SDR2 misses

Number of SDR3 misses

Number of SDR4 misses

Number of SDR5 misses

Number of SDR6 misses

Number of SDR7 misses

Number of SDR0 hits

Number of SDR1 hits

Number of SDR2 hits

Number of SDR3 hits

Number of SDR4 hits

Number of SDR5 hits

Number of SDR6 hits

Number of SDR7 hits