Intel

®

IXP42X product line and IXC1100 control plane processors—Ethernet MAC A

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

440 Order Number: 252480-006US

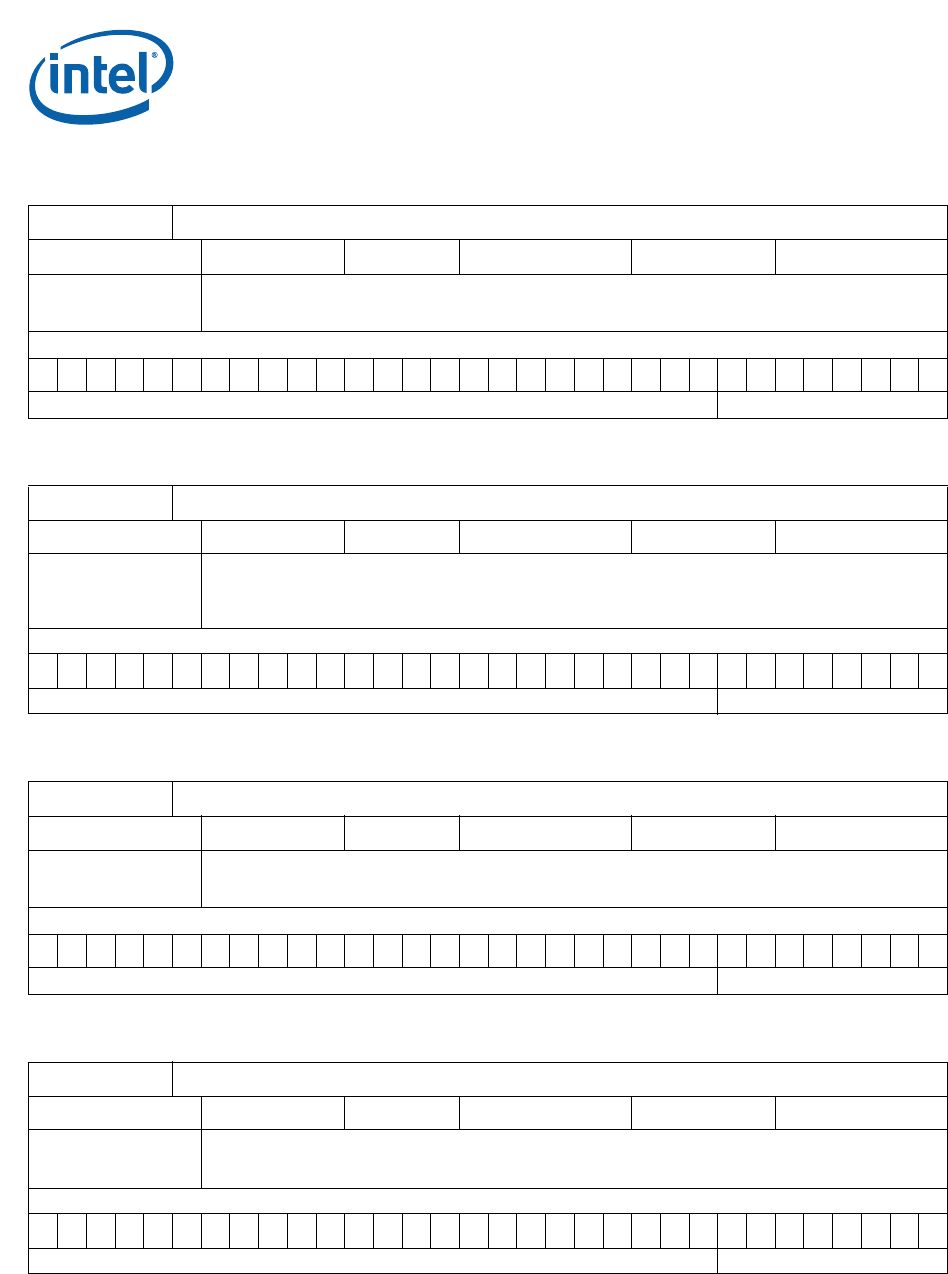

15.2.32 Address 1

15.2.33 Address 2

15.2.34 Address 3

15.2.35 Address 4

Register Name: addr1

Hex Offset Address: 0x C80090C0 Reset Hex Value: 0x00000000

Register

Description:

Address Register #1. First register of six that makes up the Address. Address Mask is used with Address

for multicast address filtering. Bits set to 1, in Address Mask, represent bits of the Address Register that

must match the corresponding bits in incoming destination addresses for packets to be accepted.

Access: Read/Write.

31 87 0

(Reserved) ADDRESS[7:0]

Register Name: addr2

Hex Offset Address: 0x C80090C4 Reset Hex Value: 0x00000000

Register

Description:

Address Register #1. Second register of six that makes up the Address. Address Mask is used with

Address for multicast address filtering. Bits set to 1, in Address Mask, represent bits of the Address

Register that must match the corresponding bits in incoming destination addresses for packets to be

accepted.

Access: Read/Write.

31 87 0

(Reserved) ADDRESS[15:8]

Register Name: addr3

Hex Offset Address: 0x C80090C8 Reset Hex Value: 0x00000000

Register

Description:

Address Register #1. Third register of six that makes up the Address. Address Mask is used with Address

for multicast address filtering. Bits set to 1, in Address Mask, represent bits of the Address Register that

must match the corresponding bits in incoming destination addresses for packets to be accepted.

Access: Read/Write.

31 87 0

(Reserved) ADDRESS[23:16]

Register Name: addr4

Hex Offset Address: 0x C80090CC Reset Hex Value: 0x00000000

Register

Description:

Address Register #1. Forth register of six that makes up the Address. Address Mask is used with Address

for multicast address filtering. Bits set to 1, in Address Mask, represent bits of the Address Register that

must match the corresponding bits in incoming destination addresses for packets to be accepted.

Access: Read/Write.

31 87 0

(Reserved) ADDRESS[31:24]