Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 211

PCI Controller—Intel

®

IXP42X product line and IXC1100 control plane processors

target interface — in conjunction with the target interface FIFOs — will use the South

AHB Master interface of the PCI Controller to provided read and write access to AHB

agents, PCI Controller PCI Configuration registers (through Configuration cycles). The

PCI Controller Configuration and Status Registers accessible through Target

transactions will be accessed directly from the PCI-Target Interface.

Table 97 lists the supported command types, when the IXP42X product line and

IXC1100 control plane processors are used as a target of a PCI transaction. The PCI

Target interface does not support the following features:

• Lock cycles

• VGA palette snoop

• Dual address cycles

• Cache-line wrap mode addressing (Disconnected after first data phase of

transaction)

• Type 1 Configuration space

When the IXP42X product line and IXC1100 control plane processors want to use an

external PCI device as the target of a PCI transfer, the PCI Controller Initiator interface

will be used to generate the appropriate PCI bus cycles and forward the information to

the PCI bus. There are three ways in which PCI bus cycles may be initiated:

— The DMA channels generate PCI Memory cycles. Refer to “PCI Controller DMA

Controller” on page 234 for additional details.

— AHB masters generate PCI Memory cycles using memory-mapped direct access

on the AHB bus. Refer to “Example: AHB Memory Base Address Register, AHB

I/O Base Address Register, and PCI Memory Base Address Register” on

page 220 for additional details.

— Interrupt Acknowledge, Special Cycle, I/O, Configuration, and single-data-

phase Memory cycles are generated indirectly by AHB masters using a Non-

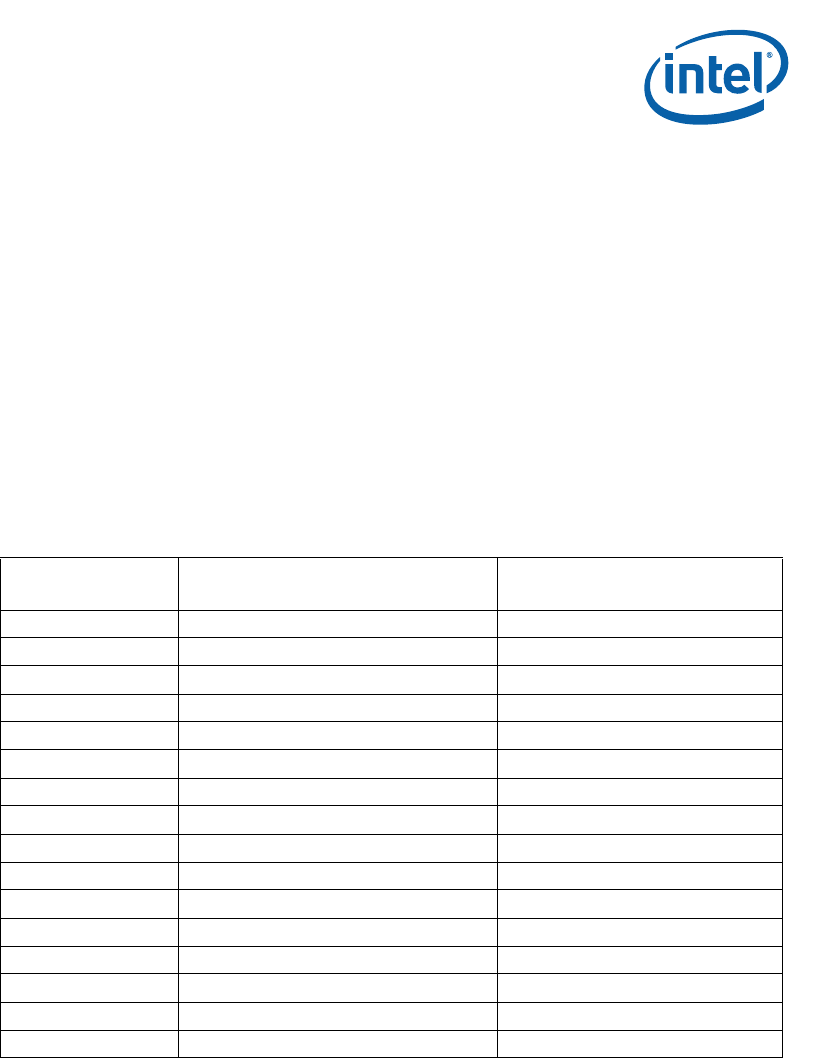

Table 97. PCI Target Interface Supported Commands

PCI Command/Byte

Enables

Command Type Support

0x0 Interrupt Acknowledge Not Supported

0x1 Special Cycle Not Supported

0x2 I/O Read Supported

0x3 I/O Write Supported

0x4 (Reserved)

0x5 (Reserved)

0x6 Memory Read Supported

0x7 Memory Write Supported

0x8 (Reserved)

0x9 (Reserved)

0xA Configuration Read Supported

0xB Configuration Write Supported

0xC Memory Read Multiple Converted To Memory Read

0xD Dual Address Cycle Not Supported

0xE Memory Read Line Converted To Memory Read

0xF Memory Write and Invalidate Converted To Memory Write