Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

September 2006 DM

Order Number: 252480-006US 261

PCI Controller—Intel

®

IXP42X product line and IXC1100 control plane processors

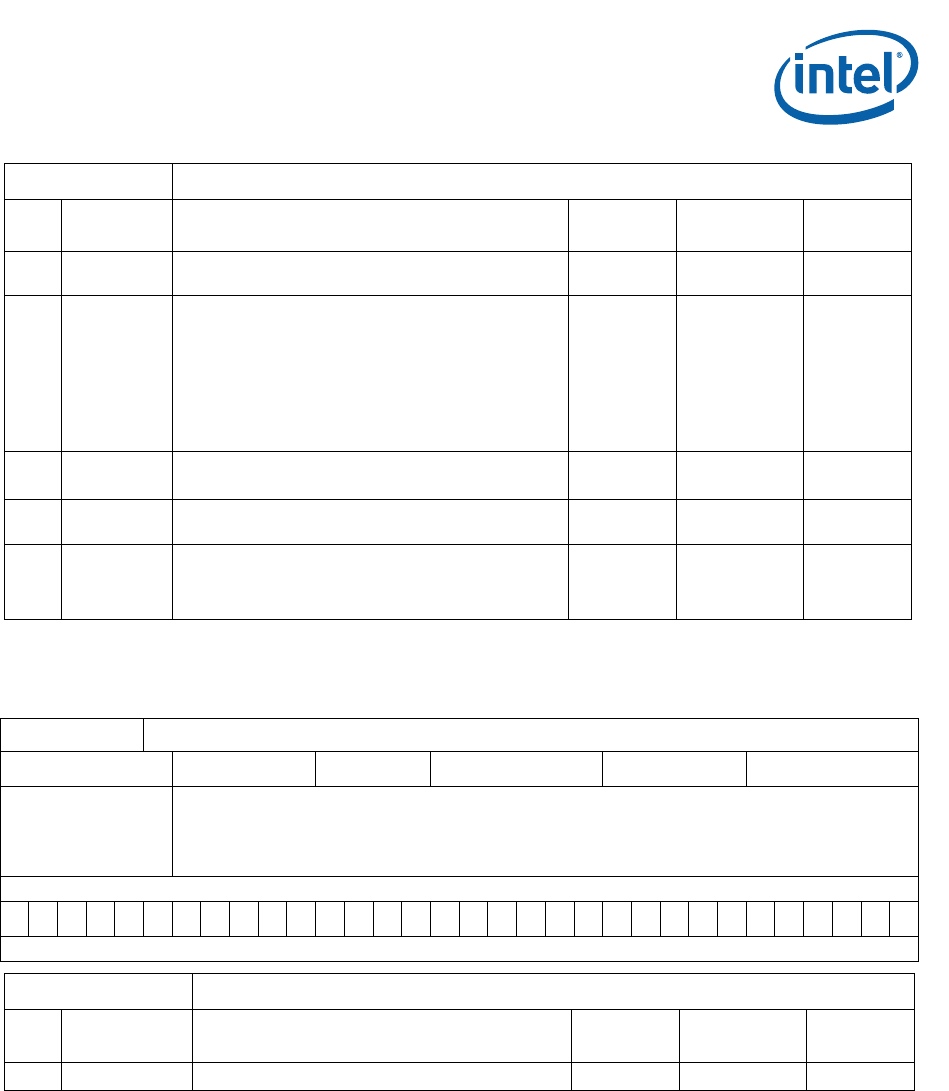

6.14.2.6 PCI Controller Configuration Port Write Data Register

(PCI_CRP_WDATA)

Register PCI_CRP_AD_CBE

Bits Name Description

Reset

Value

PCI Access AHB Access

31:2

4

(Reserved) – Read as 0 0x00 RO RO

23:2

0

CRP_BE

Active-low byte enables for a PCI configuration port

write access. This field corresponds to byte lanes in

the pci_crp_wdata register and addressed PCI

configuration register as follows:

CRP_BE[0] à bits 7:0

CRP_BE[1] à bits 15:8

CRP_BE[2] à bits 23:16

CRP_BE[3] à bits 31:24

0x0 RO RW

19:1

6

CRP_CMD

Command for the PCI configuration port access.

xxx0 = read, xxx1 = write

0x0 RO RW

15:1

1

(Reserved) – Read as 0 00000 RO RO

10:0 CRP_AD

Byte address for the PCI configuration port access.

PCI configuration registers are word-addressed so bits

1 and 0 should always be 0. Bits 10:8 specify the

function number and must always be 000.

0x000 RO RW

Register Name: PCI_CRP_WDATA

Hex Offset Address: 0xC0000014 Reset Hex Value: 0x00000000

Register

Description:

PCI configuration port write data register. Provides write data for CSR-initiated accesses of the PCI

Controller PCI configuration registers in the PCI Core. If the pci_crp_ad_cmd_be.CRP_CMD[16] bit is 1

(write), a write to pci_crp_wdata will initiate a write to the PCI Controller PCI configuration register

addressed by pci_crp_ad_cmd_be.CRP_AD[7:2]. The pci_crp_ad_cmd_be.CRP_BE field determines

which bytes are affected.

Access: See below.

31 0

CRP_WDATA

Register

PCI_CRP_WDATA

Bits Name Description

Reset

Value

PCI Access AHB Access

31:0 CRP_WDATA Write data for the configuration port write access. 0x00000000 RO RW