Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

112 Order Number: 252480-006US

3.6.13.1.1 Exception Message Byte

When any kind of exception occurs, an exception message is placed in the trace buffer.

In an exception message byte, the message type bit (M) is always 0.

The vector exception (VVV) field is used to specify bits[4:2] of the vector address

(offset from the base of default or relocated vector table). The vector allows the host

SW to identify which exception occurred.

The incremental word count (CCCC) is the instruction count since the last control flow

change (not including the current instruction for undef, SWI, and pre-fetch abort). The

instruction count includes instructions that were executed and conditional instructions

that were not executed due to the condition of the instruction not matching the CC

flags.

A count value of 0 indicates that 0 instructions executed since the last control flow

change and the current exception. For example, if a branch is immediate followed by a

SWI, a direct branch exception message (for the branch) is followed by an exception

message (for the SWI) in the trace buffer. The count value in the exception message

will be 0, meaning that 0 instructions executed after the last control flow change (the

branch) and before the current control flow change (the SWI). Instead of the SWI, if an

IRQ was handled immediately after the branch (before any other instructions

executed), the count would still be 0, since no instructions executed after the branch

and before the interrupt was handled.

A count of 0b1111 indicates that 15 instructions executed between the last branch and

the exception. In this case, an exception was either caused by the 16th instruction (if it

is an undefined instruction exception, pre-fetch abort, or SWI) or handled before the

16th instruction executed (for FIQ, IRQ, or data abort).

3.6.13.1.2 Non-Exception Message Byte

Non-exception message bytes are used for direct branches, indirect branches, and

rollovers.

In a non-exception message byte, the four-bit message type field (MMMM) specifies the

type of message (refer to Table 49).

The incremental word count (CCCC) is the instruction count since the last control flow

change (excluding the current branch). The instruction count includes instructions that

were executed and conditional instructions that were not executed due to the condition

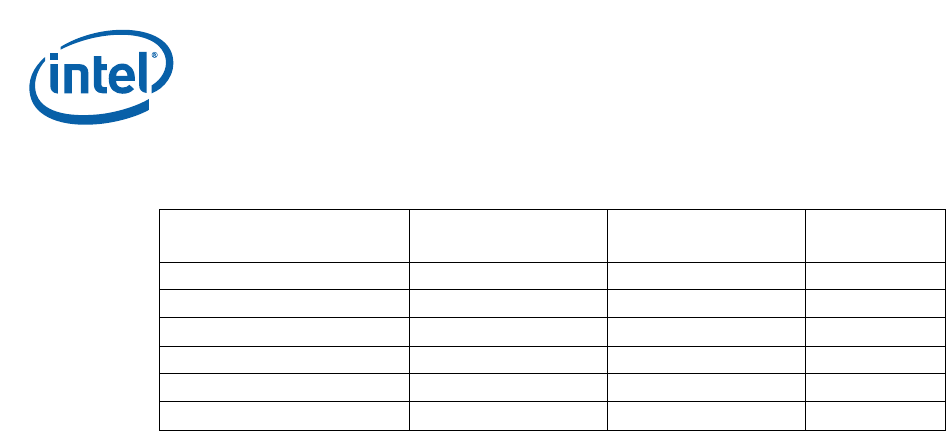

Table 49. Message Byte Formats

Message Name Message Byte Type Message Byte Format

# Address

Bytes

Exception exception 0b0VVV CCCC 0

Direct Branch

1

non-exception 0b1000 CCCC 0

Check-Pointed Direct Branch

1

non-exception 0b1100 CCCC 0

Indirect Branch

2

non-exception 0b1001 CCCC 4

Check-Pointed Indirect Branch

2

non-exception 0b1101 CCCC 4

Roll-over non-exception 0b1111 1111 0

Notes:

1. Direct branches include ARM and Thumb bl, b.

2. Indirect branches include ARM ldm, ldr, and dproc to PC; ARM and Thumb bx, blx(1) and blx(2); and

Thumb pop.