Intel

®

IXP42X product line and IXC1100 control plane processors—Universal Serial Bus (USB)

v1.1 Device Controller

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

516 Order Number: 252480-006US

18.5.18 UDC Interrupt Control Register 0 (UICR0)

The UICR0 contains eight control bits to enable/disable interrupt service requests from

data endpoints 0 - 7. All of the UICR0 bits are reset to a 1 so interrupts are not

generated on initial system reset.

18.5.18.1 Interrupt Mask Endpoint x (IMx), Where x is 0 through 7

The UICR0[IMx] bit is used to mask or enable the corresponding endpoint interrupt

request, USIR0[IRx]. When the mask bit is set, the interrupt is masked and the

corresponding bit in the USIR0 register is not allowed to be set.

When the mask bit is cleared and an interruptible condition occurs in the endpoint, the

appropriate interrupt bit is set. Programming the mask bit to a 1 does not affect the

current state of the interrupt bit. It only blocks future 0-to-1 transitions of the interrupt

bit.

Register UDCCS15

Bits Name Description

31:8 Reserved for future use.

7TSP

Transmit short packet (read/write 1 to set).

1 = Short packet ready for transmission.

6 (Reserved). Always reads 0.

5FST

Force STALL (read/write).

1 = Issue STALL handshakes to IN tokens.

4SST

Sent STALL (read/write 1 to clear).

1 = STALL handshake was sent.

3TUR

Transmit FIFO underrun (read/write 1 to clear).

1 = Transmit FIFO experienced an underrun.

2FTF

Flush Tx FIFO (always read 0/ write a 1 to set).

1 = Flush Contents of TX FIFO.

1TPC

Transmit packet complete (read/write 1 to clear).

0 = Error/status bits invalid.

1 = Transmit packet has been sent and error/status bits are valid.

0TFS

Transmit FIFO service (read-only).

0 = Transmit FIFO has no room for new data.

1 = Transmit FIFO has room for 1 complete data packet.

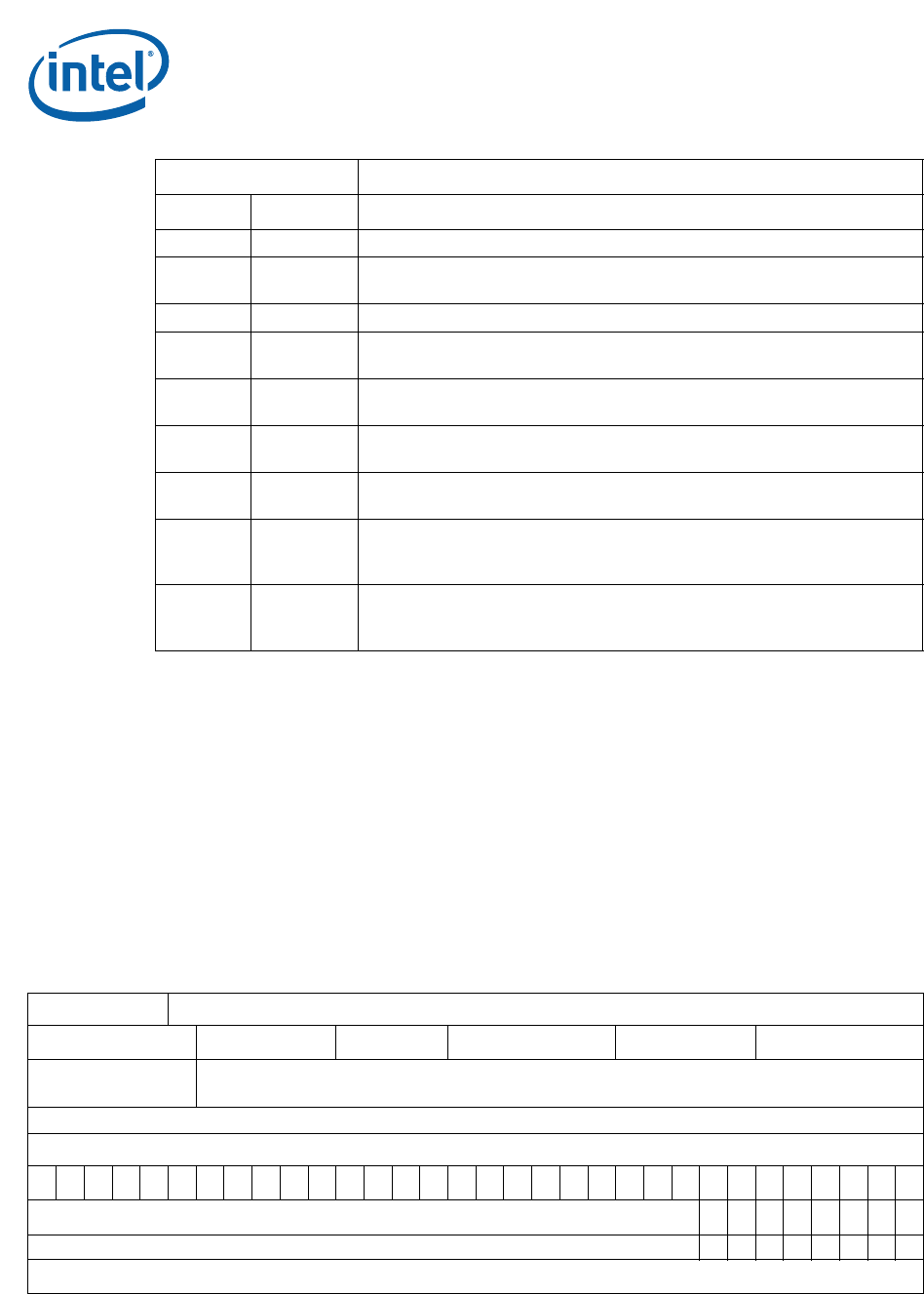

Register Name: UICR0

Hex Offset Address: 0 x C800B050 Reset Hex Value: 0x000000FF

Register

Description:

Universal Serial Bus Device Controller Interrupt Control Register 0

Access: Read/Write and Read-Only

Bits

31 876543210

(Reserved)

IM7

IM6

IM5

IM4

IM3

IM2

IM1

IM0

X 11111111

Resets (Above)