Intel

®

IXP42X product line and IXC1100 control plane processors—Intel XScale

®

Processor

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

120 Order Number: 252480-006US

During a cold reset (in which both a processor reset and a JTAG reset occurs) it can be

guaranteed that the instruction cache will be invalidated since the JTAG reset takes the

processor out of any of the modes listed above.

During a warm reset, if a JTAG reset does not occur, the instruction cache is not

invalidated by reset when any of the above modes are active. This situation requires

special attention if code needs be downloaded during the warm reset.

Note that while Halt Mode is active, reset can invalidate the main instruction cache.

Thus debug handler code downloaded during reset can only be loaded into the mini

instruction cache. However, code can be dynamically downloaded into the main

instruction cache. (refer to “Dynamically Loading IC After Reset” on page 123).

The following sections describe the steps necessary to ensure code is correctly

downloaded into the instruction cache.

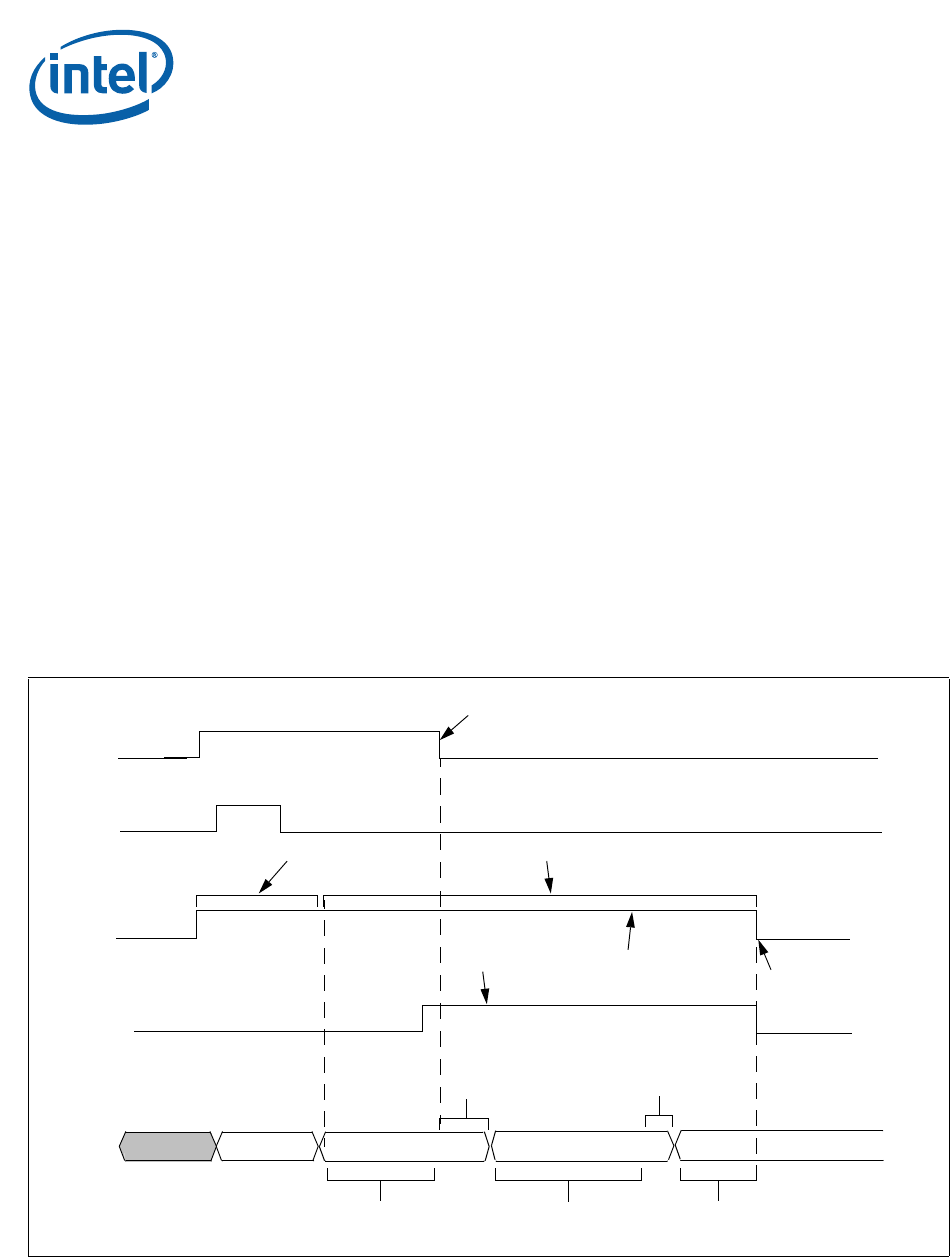

3.6.14.4.1 Loading IC During Cold Reset for Debug

The Figure 26 shows the actions necessary to download code into the instruction cache

during a cold reset for debug.

Note: In the Figure 26 hold_rst is a signal that gets set and cleared through JTAG When the

JTAG IR contains the SELDCSR instruction, the hold_rst signal is set to the value

scanned into DBG_SR[1].

An external host should take the following steps to load code into the instruction cache

following a cold reset:

1. Assert the Reset and TRST pins: This resets the JTAG IR to IDCODE and invalidates

the instruction cache (main and mini).

Figure 26. Code Download During a Cold Reset For Debug

Internal

TRST

JTAG IR

RESET invalidates IC

Enter LDIC mode

RESET does not affect IC

TRST resets JTAG IR to IDCODE

IDCODE

set hold_rst signal clear hold_rst signal

Reset Pin

RESET

RESET pin asserted until hold_rst signal is set

Processor branches

hold_rst

hold_rst keeps internal reset asserted

SELDCSR

SELDCSR

keep Halt Mode bit set

clock 15 tcks after

Download codeset Halt Mode bit

to address 0

LDIC

wait 2030 tcks after

Reset deasserted

last update_dr

in LDIC mode