Intel

®

IXP42X product line and IXC1100 control plane processors—High-Speed Serial

Interfaces

Intel

®

IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

DM September 2006

462 Order Number: 252480-006US

Every fourth timeslot received by the HSS is discarded, meaning it is not loaded into

the FIFO and is therefore not sent to the NPE.

The HSS Interface can transmit all zeros/ones (HSS programmable) for the duration of

the unassigned timeslots.

Received unassigned timeslots are not sent to the NPE as they are discarded by the

HSS.

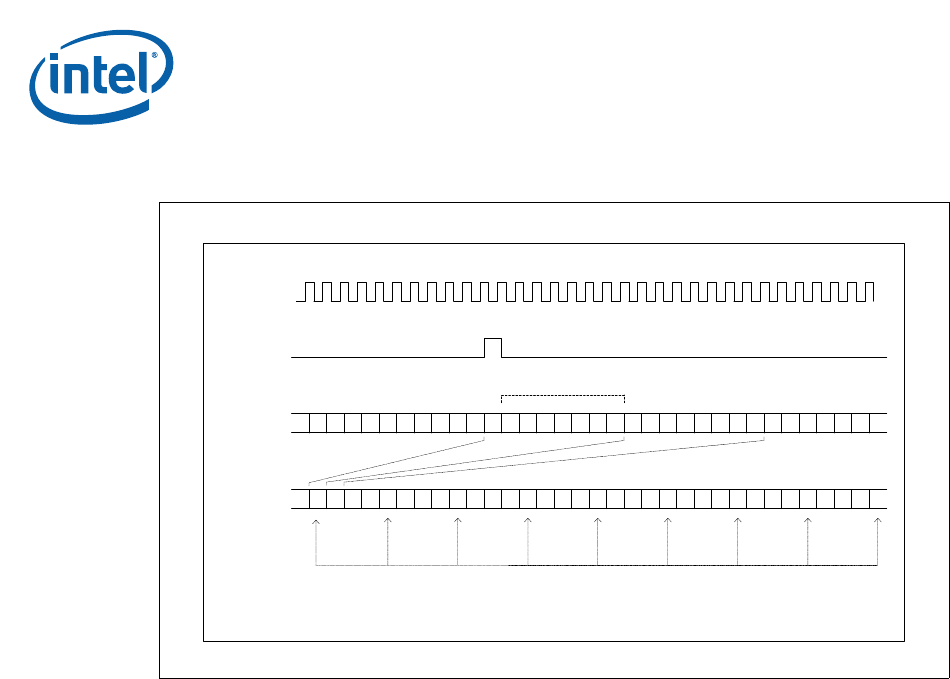

Another method of sending a T1 line over an E1 line called frame mapping is illustrated

in Figure 91. This method groups the 24 timeslots together and places unassigned

timeslots towards the end of the frame. The FBit is located at the last bit of the 32nd

timeslot, the HSS will not treat this timeslot any differently to other timeslots, it is up

the software to detect the FBit. The NPE can select which method it desires to use.

Figure 90. MVIP, Interleaved Mapping of a T1 Frame to an E1 Frame

FBi

t

XXXXXXX012345670123456

76543210765

X 0 1 2 X 3 4 5 X 6 7 8 X 9 10 11 X 12 13 14 X 15 16 17 X 18 19 20 X 21 22 23

Timeslot

Bits

Unused timeslots

23 X

2.048

MHz clock

Frame pulse

Note that in timeslot 0, the frame timeslot is not ignored

ignored