7-22 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Configuration

7.3.4 Registers 8-15: Software Debug

Software debug is supported by address breakpoint registers (Coprocessor 15, register 14), serial

communication over the JTAG interface and a trace buffer. Registers 8 and 9 are used for the serial

interface and registers 10 through 13 support a 256 entry trace buffer. Register 14 and 15 are the

debug link register and debug SPSR (saved program status register). These registers are explained

in more detail in Chapter 13, “Software Debug”.

Opcode_2 and CRm should be zero.

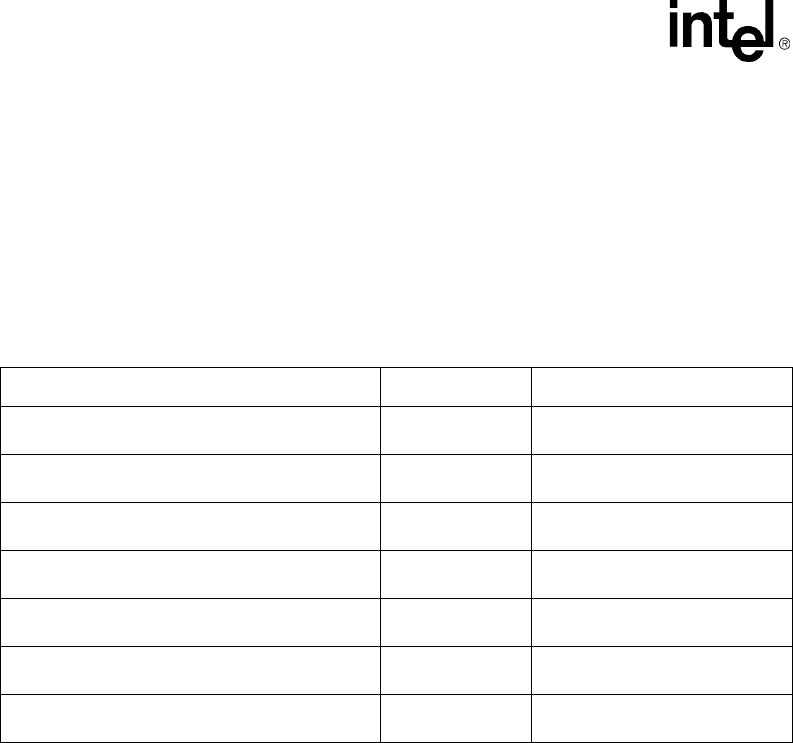

Table 7-26. Accessing the Debug Registers

Function CRn (Register #) Instruction

Access Transmit Debug Register (TX) 0b1000

MRC p14, 0, Rd, c8, c0, 0

MCR p14, 0, Rd, c8, c0, 0

Access Receive Debug Register (RX) 0b1001

MCR p14, 0, Rd, c9, c0, 0

MRC p14, 0, Rd, c9, c0, 0

Access Debug Control and Status Register

(DBGCSR)

0b1010

MCR p14, 0, Rd, c10, c0, 0

MRC p14, 0, Rd, c10, c0, 0

Access Trace Buffer Register (TBREG) 0b1011

MCR p14, 0, Rd, c11, c0, 0

MRC p14, 0, Rd, c11, c0, 0

Access Checkpoint 0 Register (CHKPT0) 0b1100

MCR p14, 0, Rd, c12, c0, 0

MRC p14, 0, Rd, c12, c0, 0

Access Checkpoint 1 Register (CHKPT1) 0b1101

MCR p14, 0, Rd, c13, c0, 0

MRC p14, 0, Rd, c13, c0, 0

Access Transmit and Receive Debug Control

Register

0b1110

MCR p14, 0, Rd, c14, c0, 0

MRC p14, 0, Rd, c14, c0, 0