Developer’s Manual March, 2003 11-7

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Bus Controller

When ECC is enabled, the BCU only generates an interrupt on a single-bit error if BCUCTL.SR is

set. When ECC is enabled, the BCU always generates an abort on a multi-bit error.

The BCU repairs single bit errors if BCUCTL.SC is set. It is recommended that this bit always be

set; running with this bit cleared could cause software to operate on corrupted data before the

ECC-error detect interrupt is received.

If BCUCTL.EE is zero, then the BCU ignores the ECC bits on reads and drives all zeroes to the

ECC bits on writes. This is the fastest mode for the BCU, as ECC error detection/correction incurs

an additional two MCLK cycles.

If error reporting is enabled in BCUCTL, and any of the bits BCUCTL.EV, BCUCTL.E1,

BCUCTL.E0 are set, then the BCU asserts its interrupt to the ICU on a single-bit error. These bits

are set by the BCU when it detects an error and saves the error information to ELOGx and ECARx.

If BCUCTL.En is set (n = 0,1), the BCU does not alter the contents of registers ELOGn and

ECARn. This ensures that software can use these registers until it clears BCUCTL.En.

These bits may be used by an ISR to quickly determine how many errors have occurred, and to

locate the error information in other registers (ELOGx and ECARx). To clear the BCU’s interrupt,

an ISR must ensure that all of these bits are cleared. Pseudocode for a typical ISR that handles

BCU Errors is shown in Example 11-3.

It is possible for more errors to occur while clearing the existing errors. In this case, the ISR is

reinvoked as soon as BCU interrupts are unmasked.

The BCU Control Register (BCUCTL) allows software to view and control the behavior of the BCU.

Example 11-3. Handling BCU Errors

if(BCUCTL.EV)

... more errors that couldn’t be logged -- react to them here

BCUCTL.EV = 1 clear the EV bit -- error is handled

if(BCUCTL.E1)

... react to error here

BCUCTL.E1 = 1 clear the E1 bit -- error is handled

if(BCUCTL.E0)

... react to error here

BCUCTL.E0 = 1 clear the E0 bit -- error is handled

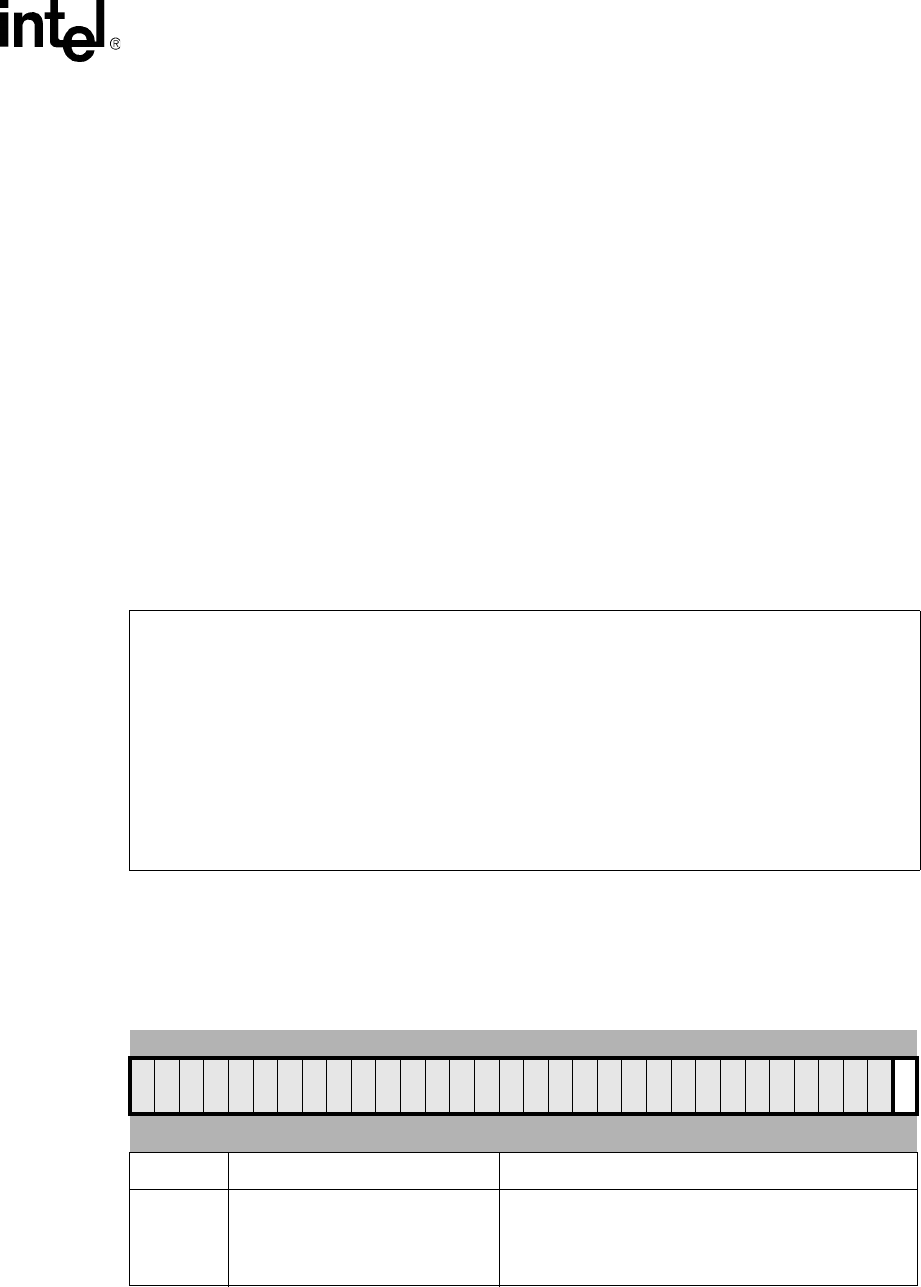

Table 11-3. BCUMOD (Register 1)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

A

F

reset value: all implemented bits are 0

Bits Access Description

0 Read-unpredictable / Write

AF - Aligned Fetch

0 = On a 32-byte read, BCU requests an aligned block

1 = BCU can request 32-byte reads on any 4-byte

aligned address.