9-2 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Interrupts

9.3 Programmer Model

Software has access to three registers in the ICU. INTCTL is used to enable or disable (mask)

individual interrupts. As mentioned, masking of all interrupts may still be accomplished via the

CPSR register in the core. INTSRC is a read-only register that records all currently active interrupt

sources. Even if an interrupt is masked, software may use INTSRC to test for its source. INTSTR is

used to direct internal interrupts to either FIQ or IRQ.

The ICU registers reside in Coprocessor 13 (CP13). They may be accessed/manipulated with the

MCR, MRC, STC, and LDC instructions. The CRn field of the instruction denotes the register

number to be accessed. The opcode_1, opcode_2, and CRm fields of the instruction should be zero.

Most systems restricts access to CP13 to privileged processes. To control access to CP13, use the

Coprocessor Access Register (see Section 7.2.15).

An instruction that modifies an ICU register is guaranteed to take effect before the next instruction

executes. For example, if an instruction masks an interrupt source, subsequent instructions execute

in an environment in which the masked interrupt does not occur.

The details of the ICU registers are discussed in the following sections.

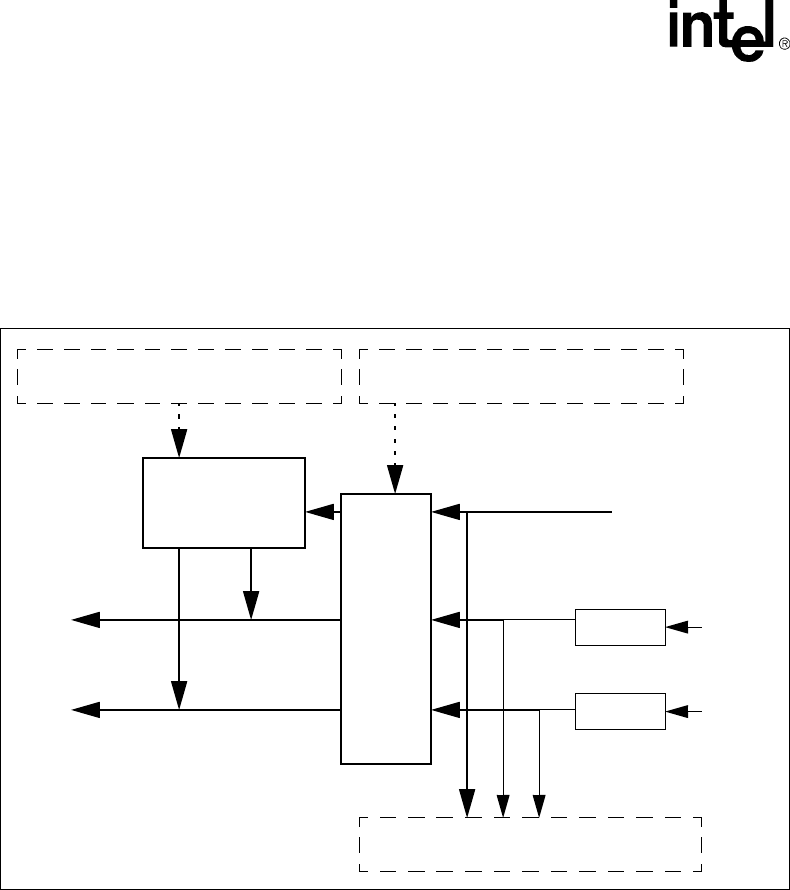

Figure 9-1. Interrupt Controller Block Diagram

FIQ# pin

IRQ# pin

(Internal Interrupt

Sources)

INTCTL Interrupt Control Register

Synch.

Synch.

INTSRC Interrupt Source Register

Mask

Logic

Mask Control

Internal Interrupt

Steering Logic

Internal FIQ

Internal IRQ

Steer Control

INTSTR Interrupt Steering Register