Developer’s Manual March, 2003 C-7

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Test Features

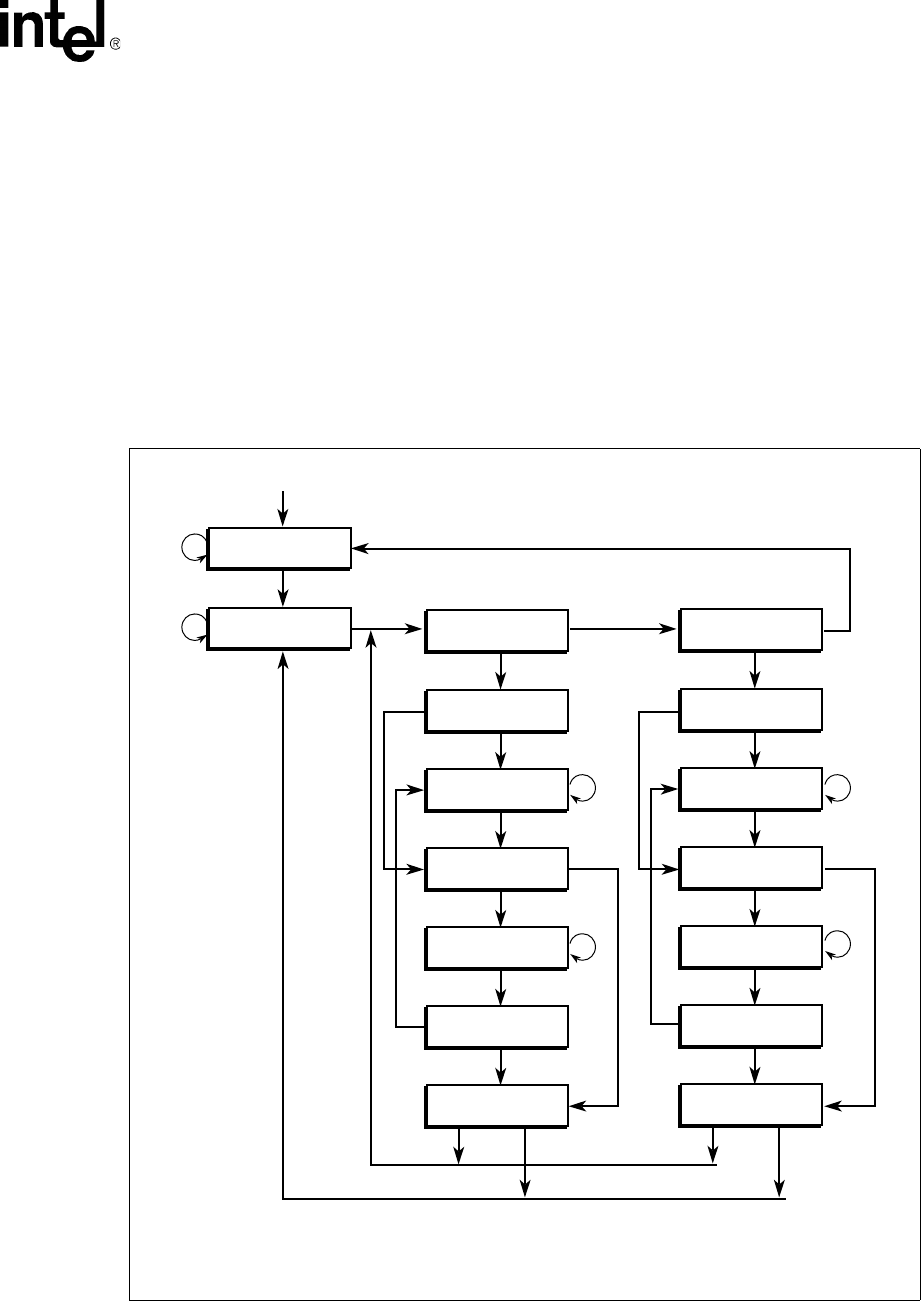

C.2.5 TAP Controller

The TAP controller is a 16-state synchronous finite state machine that controls the sequence of test

logic operations. The TAP can be controlled via a bus master. The bus master can be either

automatic test equipment or a component (i.e. PLD) that interfaces to the Test Access Port (TAP).

The TAP controller changes state only in response to a rising edge of TCK or power-up. The value

of the test mode state (TMS) input signal at a rising edge of TCK controls the sequence of state

changes. The TAP controller is automatically initialized on powerup. In addition, the TAP

controller can be initialized by applying a high signal level on the TMS input for five TCK periods.

Behavior of the TAP controller and other test logic in each controller state is described in the

following subsections. For greater detail on the state machine and the public instructions, refer to

IEEE 1149.1 Standard Test Access Port and Boundary-Scan Architecture Document.

Figure C-2. TAP Controller State Diagram

B1309-01

1

TEST-LOGIC-

RESET

0

1

1

1

11

0

1

1

SELECT -

DR - SCAN

0

SELECT -

IR - SCAN

0

CAPTURE - DR

0

0

0

0

RUN-TEST /

IDLE

0

CAPTURE - IR

SHIFT - DR

1

1

SHIFT - IR

EXIT1 - DR

0

0

EXIT1 - IR

PAUSE - DR

1

1

PAUSE - IR

EXIT2 - DR

1

1

EXIT2 - IR

UPDATE - DR

1

100

UPDATE - IR

NOTE: All state transitions are based on the value of TMS.

0

0

0

TRST#=0