2-8 March, 2003 Developer’s Manual

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Programming Model

The MAR instruction moves the value in register RdLo to bits[31:0] of the 40-bit accumulator

(acc0) and moves bits[7:0] of the value in register RdHi into bits[39:32] of acc0.

The instruction is only executed if the condition specified in the instruction matches the condition

code status.

This instruction executes in any processor mode.

The MRA instruction moves the 40-bit accumulator value (acc0) into two registers. Bits[31:0] of

the value in acc0 are moved into the register RdLo. Bits[39:32] of the value in acc0 are sign

extended to 32 bits and moved into the register RdHi.

The instruction is only executed if the condition specified in the instruction matches the condition

code status.

This instruction executes in any processor mode.

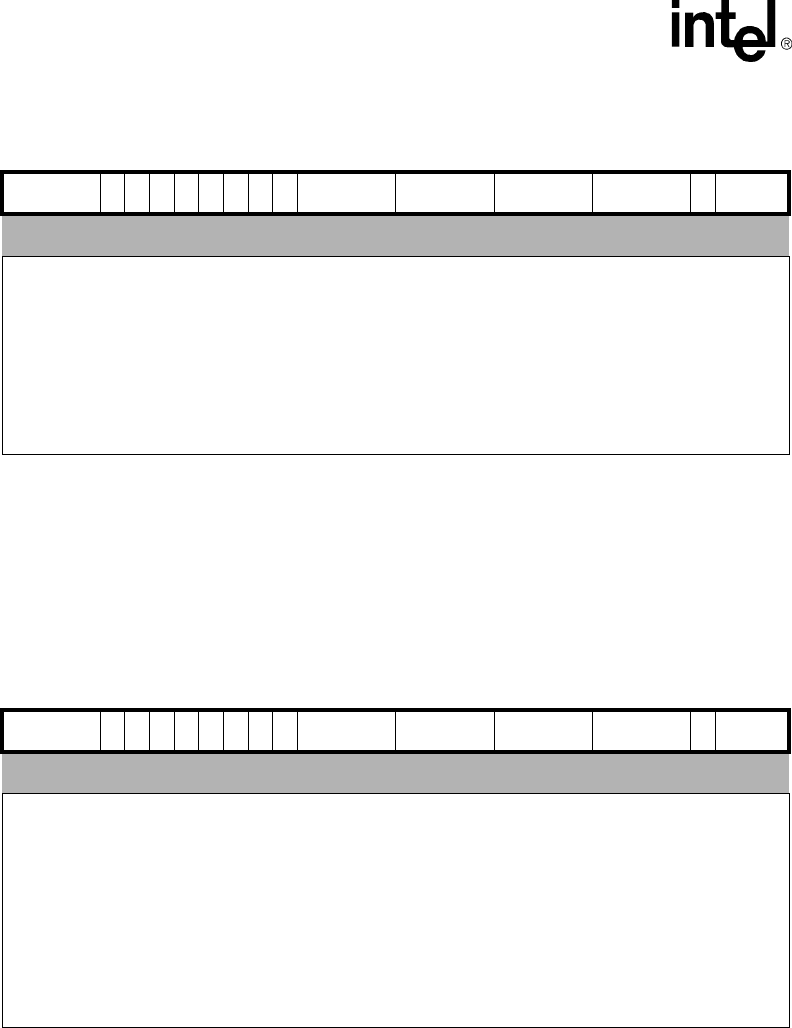

Table 2-6. MAR{<cond>} acc0, RdLo, RdHi

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

cond 11000100 RdHi RdLo 000000000000

Operation: if ConditionPassed(<cond>) then

acc0[39:32] = RdHi[7:0]

acc0[31:0] = RdLo[31:0]

Exceptions:none

Qualifiers Condition Code

No condition code flags are updated

Notes: Instruction timings can be found in

Section 14.4.4, “Multiply Instruction Timings” on page 14-6

Specifying R15 as either RdHi or RdLo has unpredictable results.

Table 2-7. MRA{<cond>} RdLo, RdHi, acc0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

cond 11000101 RdHi RdLo 000000000000

Operation: if ConditionPassed(<cond>) then

RdHi[31:0] = sign_extend(acc0[39:32])

RdLo[31:0] = acc0[31:0]

Exceptions:none

Qualifiers Condition Code

No condition code flags are updated

Notes: Instruction timings can be found in

Section 14.4.4, “Multiply Instruction Timings” on page 14-6

Specifying the same register for RdHi and RdLo has unpredictable

results.

Specifying R15 as either RdHi or RdLo has unpredictable results.