Developer’s Manual March, 2003 9-5

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Interrupts

9.3.3 INTSTR

Systems may have differing priorities for the various interrupt cases; the ICU allows system

designers to associate each internal interrupt source with one of the two internal interrupts: FIQ and

IRQ. This association is called steering.

INTSTR is used to specify how internal interrupt sources should be steered

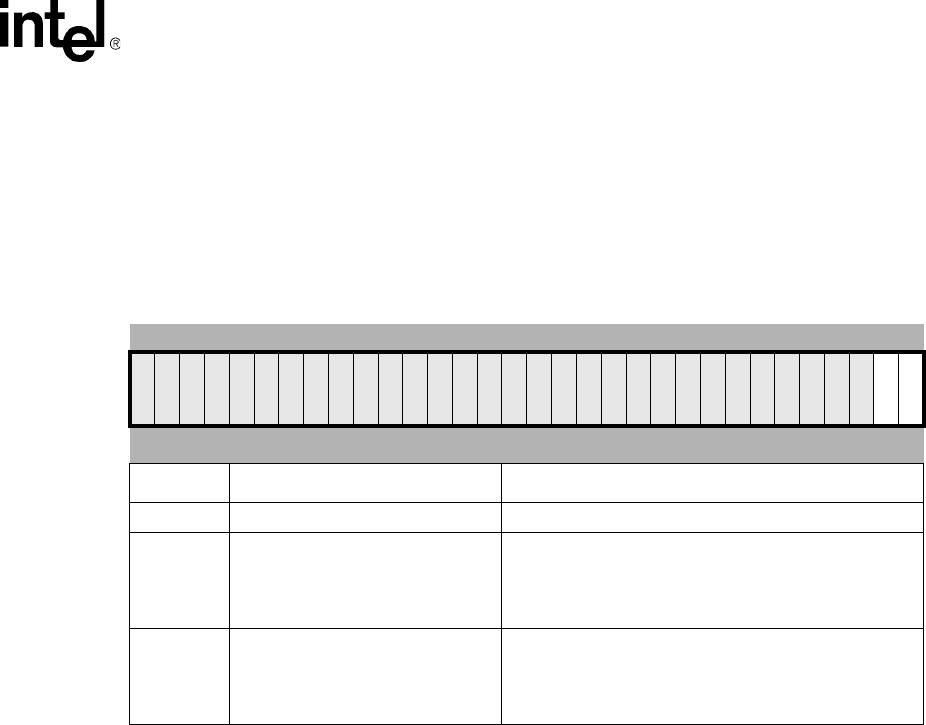

Table 9-3. Interrupt Steer Register (CP13, register 8)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

B

S

P

S

reset value: writeable bits set to 0

Bits Access Description

31:2 Read-unpredictable / Write-as-Zero Reserved

1 Read / Write

BS - BCU Steering

If BCU interrupts are enabled, this bit steers them.

0 = BCU interrupts directed to internal IRQ

1 = BCU interrupts directed to internal FIQ

0 Read / Write

PS - PMU Steering

If PMU interrupts are enabled, this bit steers them.

0 = PMU interrupts directed to internal IRQ

1 = PMU interrupts directed to internal FIQ