Developer’s Manual March, 2003 13-27

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Software Debug

When the trace buffer is enabled, reading and writing to either checkpoint register has

unpredictable results. When the trace buffer is disabled, writing to a checkpoint register sets the

register to the value written. Reading the checkpoint registers returns the value of the register.

In normal usage, the checkpoint registers are used to hold target addresses of specific entries in the

trace buffer. Only direct and indirect entries get checkpointed. Exception and roll-over messages

are never checkpointed. When an entry is checkpointed, the processor sets bit 6 of the message

byte to indicate this (refer to Table 13-17., Message Byte Formats)

When the trace buffer contains only one checkpointed entry, the corresponding checkpoint register

is CHKPT0. When the trace buffer wraps around, two entries are typically checkpointed, usually

about half a buffers length apart. In this case, the first (oldest) checkpointed entry read from the

trace buffer corresponds to CHKPT1, the second checkpointed entry corresponds to CHKPT0.

Although the checkpoint registers are provided for wrap-around mode, they are still valid in

fill-once mode.

13.12.1.2 Trace Buffer Register (TBREG)

The trace buffer is read through TBREG, using MRC and MCR. Software should only read the

trace buffer when it is disabled. Reading the trace buffer while it is enabled, may cause

unpredictable behavior of the trace buffer. Writes to the trace buffer have unpredictable results.

Reading the trace buffer returns the oldest byte in the trace buffer in the least significant byte of

TBREG. The byte is either a message byte or one byte of the 32 bit address associated with an

indirect branch message.Table 13-16 shows the format of the trace buffer register.

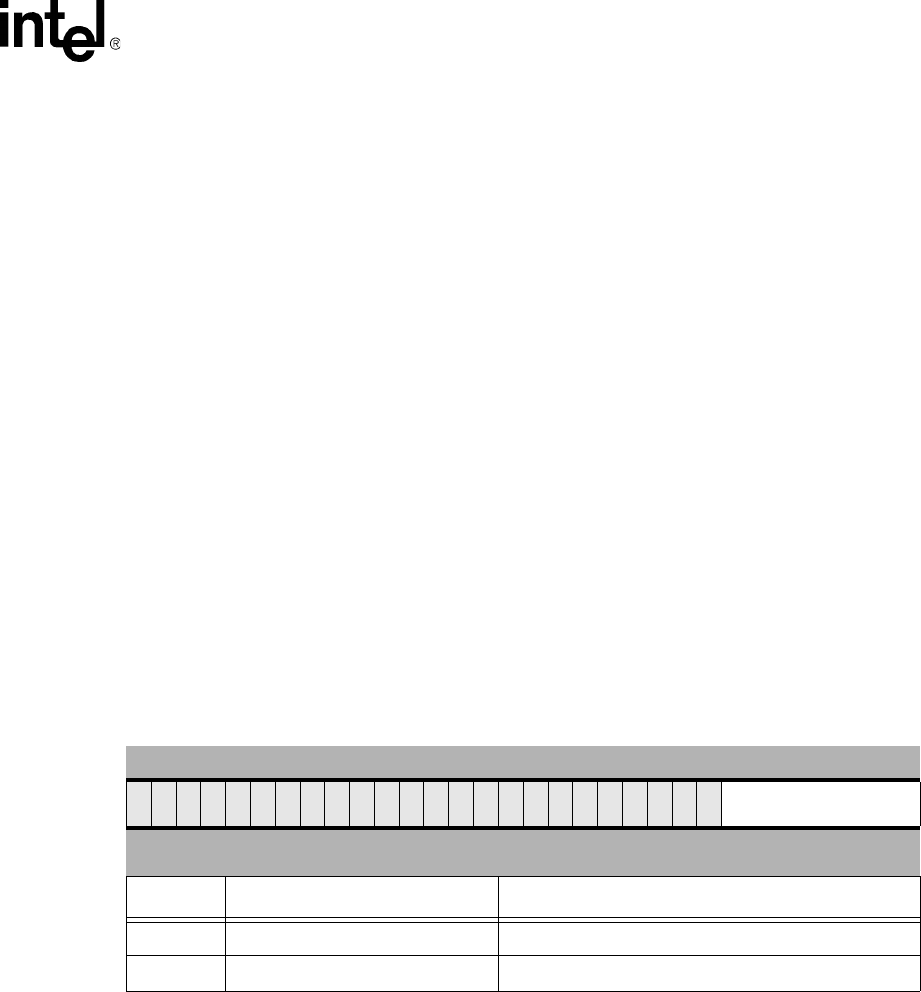

Table 13-16. TBREG Format

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Data

reset value: unpredictable

Bits Access Description

31:8 Read-as-Zero/Write-ignored Reserved

7:0 Read / Write-unpredictable Message Byte or Address Byte