Developer’s Manual March, 2003 13-19

Intel

®

80200 Processor based on Intel

®

XScale

™

Microarchitecture

Software Debug

13.11.2.1 DBG.HLD_RST

The debugger uses DBG.HLD_RST when loading code into the instruction cache during a

processor reset. Details about loading code into the instruction cache are in Section 13.14,

Downloading Code in the ICache.

The debugger must set DBG.HLD_RST before or during assertion of the reset pin. Once

DBG.HLD_RST is set, the reset pin can be de-asserted, and the processor internally remains in

reset. The debugger can then load debug handler code into the instruction cache before the

processor begins executing any code.

Once the code download is complete, the debugger must clear DBG.HLD_RST. This takes the

processor out of reset, and execution begins at the reset vector.

A debugger sets DBG.HLD_RST in one of 2 ways:

• Either by taking the JTAG state machine into the Capture_DR state, which automatically loads

DBG_SR[1] with ‘1’, then the Exit2 state, followed by the Update_Dr state. This sets the

DBG.HLD_RST, clear DBG.BRK, and leave the DCSR unchanged (the DCSR bits captured in

DBG_SR[34:3] are written back to the DCSR on the Update_DR).

• Alternatively, a ‘1’ can be scanned into DBG_SR[1], with the appropriate value scanned in for

the DCSR and DBG.BRK.

DBG.HLD_RST can only be cleared by scanning in a ‘0’ to DBG_SR[1] and scanning in the

appropriate values for the DCSR and DBG.BRK.

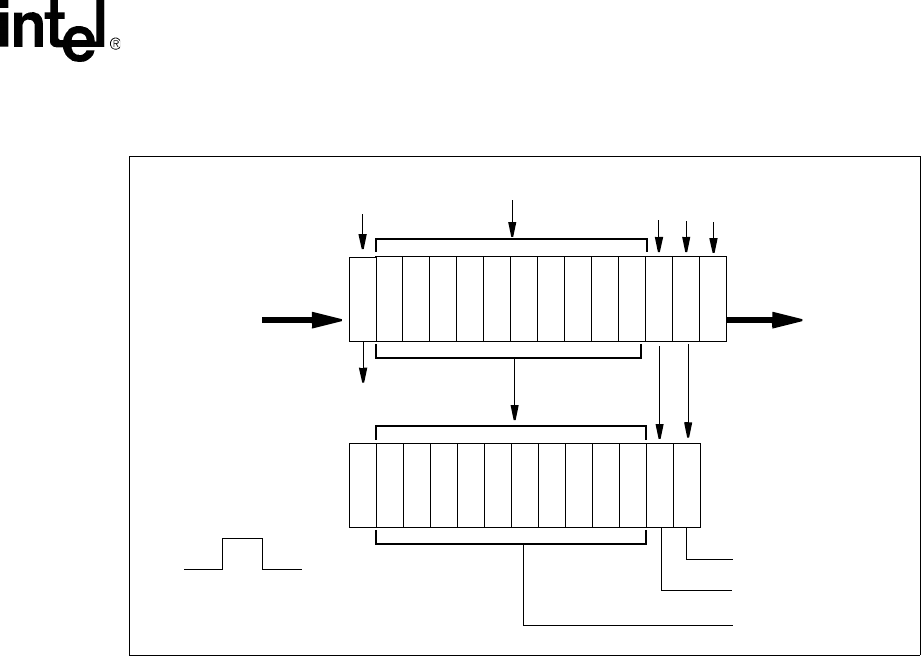

Figure 13-2. SELDCSR Data Register

12

3334

TDO

TDI

DBG_SR

Capture_DR

Update_DR

DBG_REG

1233435

TCK

0

0

DCSR

DBG.HLD_RST

DBG.DCSR

0

0

1

DBG.BRK

0

ignored